07/Jun/2006

# **GENERAL SPECIFICATION**

# MODULE NO. :

# DEM 128064A FGH-PW

CUSTOMER P/N

| VERSION NO. | CHANGE DESCRIPTION                                        | DATE        |

|-------------|-----------------------------------------------------------|-------------|

| 0           | ORIGINAL VERSION                                          | 18/12/2002  |

| 1           | THE EXTERNAL DIMENSIONS<br>CHANGED                        | 14/01/2003  |

| 2           | ADD VERSION                                               | 06/08/2003  |

| 3           | CHANGED BACKLIGHT<br>ELECTRICAL/OPTICAL<br>SPECIFICATIONS | 10/11/2004  |

| 4           | CANCEL VERSION                                            | 06/01/2004  |

| 5           | ADD VERSION                                               | 27/06/2005  |

| 6           | CHANGE BACKLIGHT RESISTOR                                 | 27/10/2005  |

| 7           | ADD VERSION                                               | 18/11/2005  |

| 8           | ADD JUMPER SETTING                                        | 07/02/2006  |

| 9           | CHANGED PCB DESCRIPTION                                   | 10/02/2006  |

| 10          | ADD VERSION                                               | 132/03/2006 |

| 11          | CANCEL VERSION                                            | 16/03/2006  |

| 12          | MODIFY SECTION 10-1                                       | 07/06/2007  |

|             |                                                           |             |

PREPARED BY: WJN

DATE: 07/06/2007 DATE: 25/06/2007

APPROVED BY: MH

# CONTENTS

| 1. FUNCTIONS & FEATURES                         | 2  |

|-------------------------------------------------|----|

| 2. MECHANICAL SPECIFICATIONS                    | 2  |

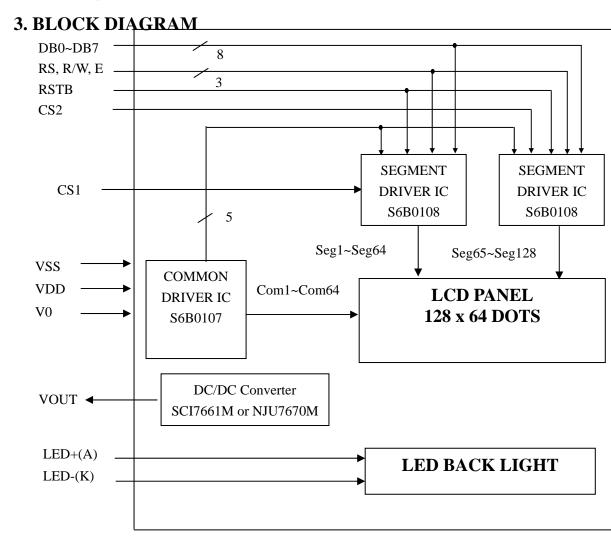

| 3. BLOCK DIAGRAM                                | 2  |

| 4. EXTERNAL DIMENSIONS                          | 3  |

| 5. PIN ASSIGNMENT                               | 3  |

| 6. PCB DRAWING AND DESCRIPTION                  | 4  |

| 7. BACKLIGHT ELECTRICAL / OPTICAL SPECIFICATION | 5  |

| 8. APPLICATION CIRCUIT                          | 6  |

| 9. MAXIMUM ABSOLUTE LIMIT                       | 6  |

| 10. ELECTRICAL CHARACTERISTICS                  | 7  |

| 11. OPERATING PRINCIPLES & METHODS              | 9  |

| 12. DISPLAY CONTROL INSTRUCTION                 | 11 |

| 13. LCD MODULES HANDLING PRECAUTIONS            | 13 |

| 14. OTHERS                                      | 13 |

### **1. FUNCTIONS & FEATURES**

|   | MODULE                                        | LCD TYPE                               |

|---|-----------------------------------------------|----------------------------------------|

|   | DEM 128064A FGH-PW                            | FSTN Transflective Positive Mode       |

|   |                                               |                                        |

| • | Viewing Direction                             | : 6 o'clock                            |

| • | Driving Scheme                                | : 1/64 Duty Cycle, 1/9 Bias            |

| • | Power Supply Voltage                          | : 5.0 Volt (typ.)                      |

| • | V <sub>LCD</sub> Adjustable for Best Contrast | : 12.9 Volt (typ. @ 25°C)              |

| • | Display Format                                | : 128 x 64 Dots                        |

| • | Interface RAM                                 | : 512 bytes (4096 bits)                |

| • | Interface                                     | : 8 bit parallel display data from MPU |

| • | Operating Temperature                         | : -20°C to +70°C                       |

| • | Storage Temperature                           | $: -25^{\circ}C$ to $+75^{\circ}C$     |

|   | DC/DC Convertor                               | · NIUI7670M (or aquivalant)            |

#### • DC/DC-Converter : NJU7670M (or equivalent)

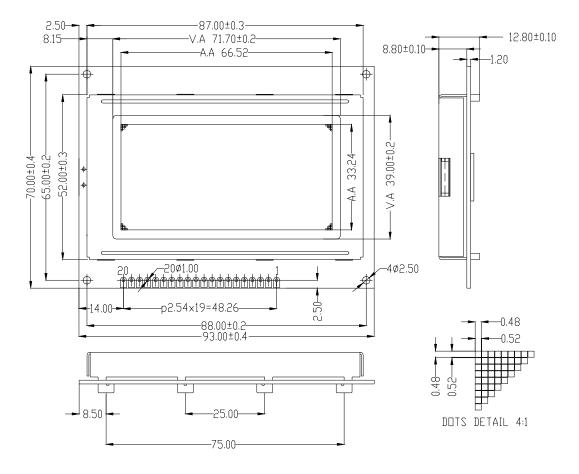

### 2. MECHANICAL SPECIFICATIONS

- Module Size

- Dot Size

- Dot Pitch

- Dot Gap

: 0.48 x 0.48 mm

: 93.00 x 70.00 x 12.8 mm

- : 0.52 x 0.52 mm

- : 0.04 mm

Version:12

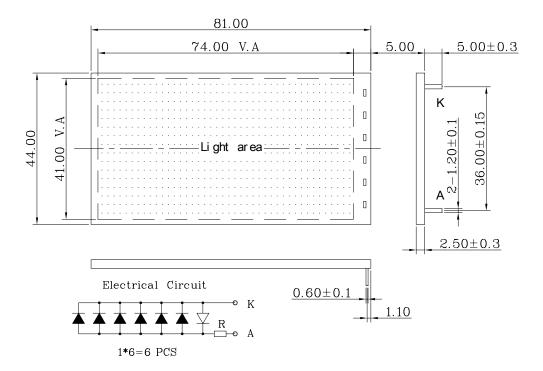

# 4. EXTERNAL DIMENSIONS

### 5. PIN ASSIGNMENT

| Pin No. | Symbol    | Function                                                                  |

|---------|-----------|---------------------------------------------------------------------------|

| 1       | VSS       | Ground                                                                    |

| 2       | VDD       | Power supply voltage for logic, (typ. 5.0 Volt).                          |

| 3       | V0        | Input voltage for LCD                                                     |

| 4       | RS        | Register select<br>RS = 0 (Instruction register) $RS = 1$ (Data register) |

| 5       | R/W       | Read /Write<br>R/W = 1 (Read) $R/W = 0$ (Write)                           |

| 6       | Е         | Chip enable signal                                                        |

| 7       | DB0       | Data bit 0                                                                |

| 8       | DB1       | Data bit 1                                                                |

| 9       | DB2       | Data bit 2                                                                |

| 10      | DB3       | Data bit 3                                                                |

| 11      | DB4       | Data bit 4                                                                |

| 12      | DB5       | Data bit 5                                                                |

| 13      | DB6       | Data bit 6                                                                |

| 14      | DB7       | Data bit 7                                                                |

| 15      | CS1       | Chip select signal for S6B0108(1)                                         |

| 16      | CS2       | Chip select signal for S6B0108(2)                                         |

| 17      | RSTB      | Reset signal                                                              |

| 18      | VOUT      | Output voltage for LCD, (-9.5Volt)                                        |

| 19      | LED + (A) | Please also refer to 6.1 Example application                              |

| 20      | LED - (K) | Please also refer to 6.1 Example application                              |

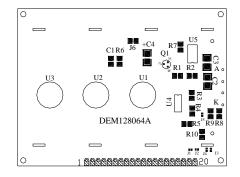

## 6. PCB DRAWING AND DESCRIPTION

#### **DESCRIPTION:**

#### 6.1.1 The polarity of the pin 19 and the pin 20:

| J2,J4 | J1,J3 | 19 Pin  | 20 Pin  |

|-------|-------|---------|---------|

| Open  | Close | Anode   | Cathode |

| Close | Open  | Cathode | Anode   |

Note: In application module, J2=J4=open, J1=J3=closed

6.1.2 The LED resistor can be bridged when the J5 is closed

Note: In application module, J5=open

6.1.3 The R8, R9 and R10 are the LED resistor.

Note: In application module, R8=R9=33Ohm, R10=open

6.1.4 The metal-bezel is set on ground when the J6 is closed.

Note: In application module, J6=closed.

6.1.5 The module number DEM128064A is printed on the PCB.

### **6.2 Example application**

6.2.1 The LED resistor should be bridged as following.

6-1-2. The 19 pin is the anode and the 20 pin is the cathode as following.

6-1-3. The 19 pin is the cathode and the 20 pin is the anode as following.

# 7. BACKLIGHT ELECTRICAL/OPTICAL SPECIFICATION

#### 7-1 BACKLIGHT ELECTRICAL/OPTICAL DESCRIPTION.

| Item                     | Symbol | MIN. | TYP. | MAX. | Unit              | Conditions                           |  |

|--------------------------|--------|------|------|------|-------------------|--------------------------------------|--|

| Forward Voltage          | Vf     |      | 4.0  |      | V                 |                                      |  |

| Forward Current          | If     |      | 90   | 120  | mA                | Vf = 4.0V                            |  |

| Power Dissipation        | Pd     |      | 0.36 |      | W                 | Vf = 4.0V                            |  |

| Reverse Voltage          | VR     |      |      | 5.0  | V                 |                                      |  |

| Reverse Current          | IR     |      |      | 0.4  | mA                |                                      |  |

| Luminous Intensity       | Lv     | 130  |      |      | cd/m <sup>2</sup> | Vf = 4.0V                            |  |

| Luminous Uniformity      | ΔLv    | 70   |      |      | %                 | Vf = 4.0V                            |  |

| Enviroiten Wennelen offi | Х      | 0.27 |      | 0.32 |                   | If $10 = 4$ Tr $25\%$ (as the thirt) |  |

| Emission Wavelength      | у      | 0.27 |      | 0.32 |                   | If=10mA, Ta=25°C (each chip)         |  |

| Backlight Color          | White  |      |      |      |                   |                                      |  |

#### 7-2. BACKLIGHT DRAWING

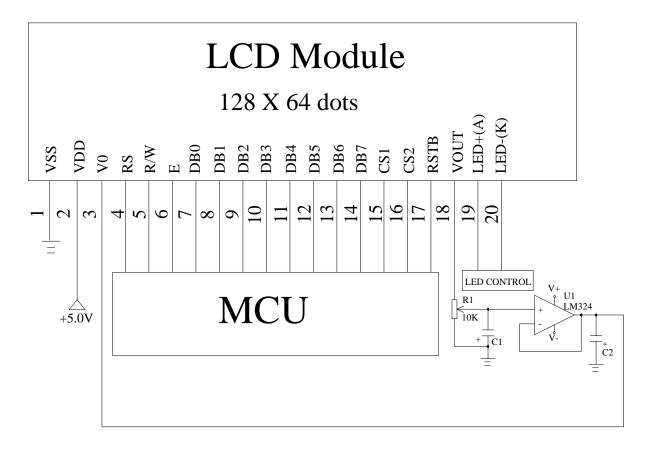

# 8. APPLICATION CIRCUIT

**NOTE:** 1. R1 is the contrast resistor.

2. VOUT=-9.5V

3. Adjust R1, it will be best contrast when V0 is -7.9V.

### 9. MAXIMUM ABSOLUTE POWER RATINGS (Ta=25°C)

| Item                     | Symbol           | Standard value                               | Unit |

|--------------------------|------------------|----------------------------------------------|------|

| Supply voltage for logic | V <sub>DD</sub>  | -0.3 ~ +7.0                                  | V    |

| Supply voltage           | V <sub>0</sub>   | V <sub>DD</sub> -19.0 ~ V <sub>DD</sub> +0.3 | V    |

| Driver supply voltage    | $V_{DD}$ - $V_0$ | $V_0 - 0.3 \sim V_{DD} + 0.3$                | V    |

| Operating temperature    | Topr             | -20 ~ +70                                    | °C   |

| Storage temperature      | Tstg             | -25 ~ +75                                    | °C   |

# **10. ELECTRICAL CHARACTERISTICS**

| Item                         | Symbol           | Stan         | dard Va | lue             | Test      | Unit |  |

|------------------------------|------------------|--------------|---------|-----------------|-----------|------|--|

| Item                         | Symbol           | MIN          | ТҮР     | MAX             | Condition | Unit |  |

| Supply current for logic     | V <sub>DD</sub>  | 4.5          | 5.0     | 5.5             |           | V    |  |

| Supply current for logic     | I <sub>DD</sub>  |              | 2.62    | 4               |           | mA   |  |

|                              | $V_{DD}$ - $V_0$ | 13.4         | 14.1    | 14.8            | -20°C     |      |  |

| Operating Voltage for<br>LCD |                  | 12.2         | 12.9    | 13.6            | 25°C      | V    |  |

|                              |                  | 11.0         | 11.7    | 12.4            | 70°C      | 1    |  |

| Input voltage "H" level      | VIH              | $0.7 V_{DD}$ |         | V <sub>DD</sub> |           | V    |  |

| Input voltage "L" level      | VIL              | 0            |         | $0.3V_{DD}$     |           | V    |  |

## **10-1 DC Characteristics (VDD=+5±10% V<sub>ss</sub>=0V,Ta=-20~+70°C)**

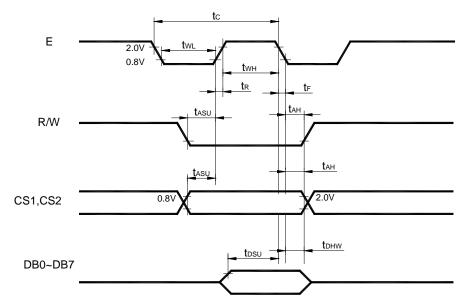

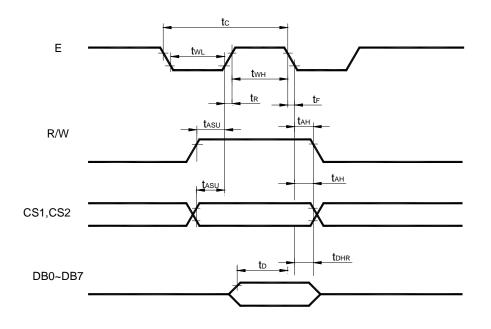

#### **10-2 MPU Interface**

| Characteristic          | Symbol           | Min  | Тур | Max | Unit |

|-------------------------|------------------|------|-----|-----|------|

| E Cycle                 | t <sub>C</sub>   | 1000 | -   | -   | ns   |

| E Rise                  | t <sub>R</sub>   | -    | -   | 25  | ns   |

| E Fall                  | t <sub>F</sub>   | -    | -   | 25  | ns   |

| E High Level Width      | t <sub>WH</sub>  | 450  | -   | -   | ns   |

| E-Low Level Width       | t <sub>WL</sub>  | 450  | -   | -   | ns   |

| Address Set –Up Time    | t <sub>ASU</sub> | 140  | -   | -   | ns   |

| Address Hold Time       | t <sub>AH</sub>  | 10   | -   | -   | ns   |

| Data Delay Time         | t <sub>D</sub>   | -    | -   | 320 | ns   |

| Data Set –Up Time       | t <sub>DSU</sub> | 200  | -   | -   | ns   |

| Data Hold Time ( Write) | t <sub>DHW</sub> | 10   | -   | -   | ns   |

| Data Hold Time (Read)   | t <sub>DHR</sub> | 20   | -   | -   | ns   |

Figure 5.0 MPU write timing

### **11. OPERATING PRINCIPLES & METHODS**

#### 11-1. I/O Buffer

Input buffer controls the status between the enable the and disable of chip. Unless the CS1 to CS2 is in active mode. Input or output of data and instruction does not execute. Therefore internal stade is not change.

Bust RSTB and ADC can operate regardless CS1-CS2.

#### 11-2. Input register

Input register is provided to interface with MPU which is different operating frequency. Input register stores the data temporarily before writing it into display RAM. When CS1 to CS2 are in the active mode, R/W and RS select the input register. The data from MPU is written into input register. Then Writing it into display RAM. Data latched for the E signal and write automatically into the display data RAM by internal operation.

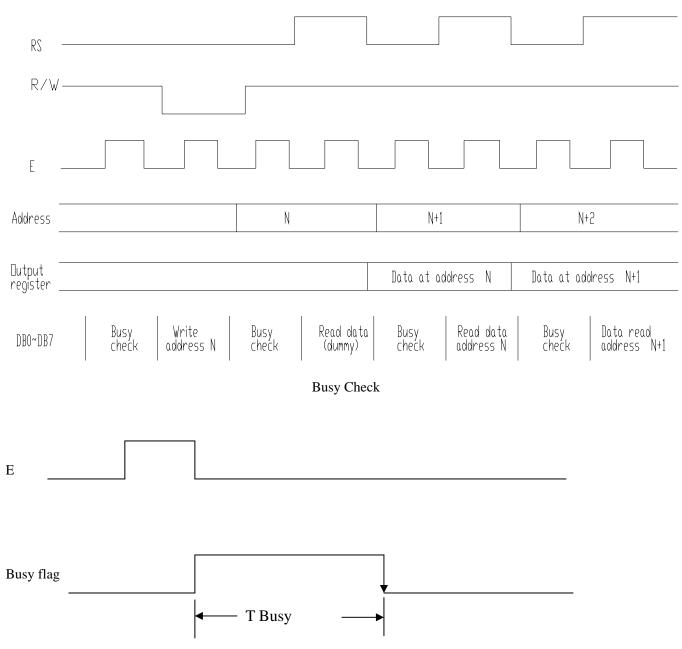

#### 11-3. Output register

Output register stores the data temporarily from display data RAM when CS1 and CS2 are in active mode and R/W and RS=H, stored data in display data RAM is latched in output register. When CS1 to CS2 are in the active mode and R/W=H, RS=L, status data (busy check) can read out. To read the contents of display data RAM, twice access of read instruction needed. In first access, data in display data RAM is latched into output register. In second access, MPU can read data which is latched. That is , to read the data in display data RAM, it needs dummy read. But staus read is not read needed dummy.

| RS | R/W | Function                                                 |

|----|-----|----------------------------------------------------------|

| т  | L   | Instruction                                              |

| L  | Н   | Status read (busy check)                                 |

| Н  | L   | Data write (from input read register to display data RAM |

|    | Н   | Data read (from display data RAM to output register)     |

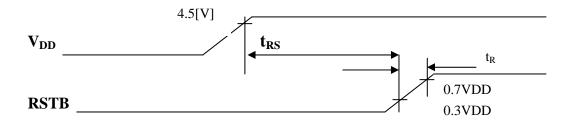

#### 11-4. Reset

The system can be initialized by setting RSTB terminal at low level when turning power on receiving instruction from RAM. When RSTB becomes low, following procedure is occurred.

- 1. Display off

- 2. Display start line register become set by 0. (Z-address 0)

While RSTB is low, No instruction except status read can be accepted. Therefore, execute other instructions after making sure than DB4=0 (clear RSTB) and DB7=0 (ready) by status read instruction.

The conditions of power supply data initial power up are shown in table 1.

Table 1. Power Supply Initial Conditions

| Item       | Symb           | Min. | Тур. | Max. | Unit |

|------------|----------------|------|------|------|------|

| Reset time | $T_{RS}$       | 1    | -    | -    | us   |

| Rise time  | t <sub>R</sub> | -    | -    | 200  | us   |

#### 11-5. Busy flag

Busy flay indicates that S6B0108 is operating or on operating. When busy flag is high, S6B0108 is internal operating. When busy flag is low, S6B0108 can accept the data or instruction.

DB7 indicates busy flag of the S6B0108.

#### 11-6. Display ON/OFF Flip-Flop

The display on/off flip-flop makes on/off the liquid crystal display. When flip-flop is reset (logical low). selective voltage or non selective voltage appears on segment output terminals. When flip-flop is set (logic high), non selective voltage appears on segment output terminals regardless of display RAM data. The display on/off flip-flop can changes status by instruction. The display data at all segment disappear while RSTB is low. The status of the flip-flop is output to DB5 by status read instruction.

#### 11-7. X Page Register

X page register designates pages of the internal display data RAM.

Count function is not available. An adders is set by instruction.

#### Version:12

#### 11-8. Y address counter

Y address counter designates address of the internal data RAM. An address is set by instruction and is increased by 1 automatically by read or write operations of display data.

#### 11-9. Display Data RAM

Display Data RAM stores a display data for liquid crystal display. To indicate on state dot matrix of liquid crystal display, write data 1. The other way, off state, writes 0.

#### 11-10. Display Start Line Register

The display start line register indicates of display data RAM to display top liquid crystal display. Bit data

(DB<0:5>) of the display start line set instruction is latched in display start line register. Latched data is transferred to the Z address counter while FRM is high, presetting the Z address counter. It is used for scrolling of the liquid crystal display screen.

### **12. DISPLAY CONTROL INSTRUCTION**

The display control instructions the internal state of the S6B0108. Instruction is received from MPU to S6B0108 for the display control. The following table shows various instructions.

| Instruction       | RS | R/W | DB7    | DB6  | DB5    | DB4        | DB3       | DB2    | DB1  | DB0 | Function                                       |

|-------------------|----|-----|--------|------|--------|------------|-----------|--------|------|-----|------------------------------------------------|

| Display<br>ON/OFF | L  | L   | L      | L    | Н      | Н          |           | Н      | Н    | L/H | Controls the display on or off. Internal       |

| 010/011           |    |     |        |      |        |            |           |        |      |     | status and display RAM                         |

|                   |    |     |        |      |        |            |           |        |      |     | data is not affected.                          |

|                   |    |     |        |      |        |            |           |        |      |     | L: OFF, H: ON                                  |

| Set Address       | L  | L   | L      | Н    | Y add  | ress (0~   | 63)       |        |      | 1   | Sets the Y address                             |

| (Y address)       |    |     |        |      |        | ``         | ,         |        |      |     | in the Y address counter.                      |

| Set Page          | L  | L   | Н      | L    | Н      | Н          | Н         | Page ( | 0~7) |     | Sets the X address                             |

| (X address)       |    |     |        |      |        |            |           |        |      |     | At the X address counter                       |

| Display Start     | L  | L   | Н      | Н    | Displa | iy start l | line (0~6 | 53)    |      |     | Indicates the                                  |

| line              |    |     |        |      |        |            |           |        |      |     | display data RAM                               |

| (Z address)       |    |     |        |      |        |            |           |        |      |     | displayed at the top of the                    |

|                   |    |     |        |      |        | 1          | •         | 1      | 1    | 1   | screen.                                        |

| Status Read       | L  | Н   | В      | L    | 0      | R          | L         | L      | L    | L   | Read status                                    |

|                   |    |     | U      |      | Ν      | E          |           |        |      |     | BUSY L: Ready                                  |

|                   |    |     | S      |      | /      | S          |           |        |      |     | H: In operation                                |

|                   |    |     | Y      |      | 0      | E          |           |        |      |     | On/Off L: display ON                           |

|                   |    |     |        |      | F      | Т          |           |        |      |     | H: Display OFF                                 |

|                   |    |     |        |      | F      |            |           |        |      |     | RESET L: Normal                                |

| XX7 ·             | TT | т   | XX7 *  |      |        |            |           |        |      |     | H: Reset                                       |

| Write             | Н  | L   | Write  | Date |        |            |           |        |      |     | Writes data (DB0:7) into                       |

| Display Data      |    |     |        |      |        |            |           |        |      |     | display data RAM . After                       |

|                   |    |     |        |      |        |            |           |        |      |     | writing instruction, Y                         |

|                   |    |     |        |      |        |            |           |        |      |     | address is increased by 1                      |

| Read              | Н  | Н   | Read I | Data |        |            |           |        |      |     | automatically.                                 |

|                   | н  | п   | Read I | Date |        |            |           |        |      |     | Reads data (DB0:7)<br>From display data PAM to |

| Display data      |    |     |        |      |        |            |           |        |      |     | From display data RAM to the data bus.         |

|                   |    |     |        |      |        |            |           |        |      |     | the trata bus.                                 |

#### 12-1. Display On/Off

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 1   | 1   | 1   | 1   | 1   | D0  |

The display data appears when D is 1 and disappears when D is 0.

Though the data is not on the screen with D=0, it remains display data RAM.

Therefore, you can make it appear by changing D=0 into D=1.

# **Product Specification**

12-2. Set Address (Y Address)

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 1   | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

Y address (AC0~AC5) of the display data RAM is set in the Y address counter.

An address is set by instruction and increased by 1 automatically by read or write operations of display data.

#### 12-3. Set Page (X Address)

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 1   | 0   | 1   | 1   | 1   | AC2 | AC1 | AC0 |

X address (AC0~AC2) of the display data RAM is set in the X address register.

Writing or reading to or from MPU is executed in this specified page until the next page is set.

#### 12-4. Display Start Line (Z Address)

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 1   | 1   | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

Z address (AC0~AC5) of the display data RAM is set in the display start line register and display at the top of the screen. When the display duty cycle is 1/64 or others ( $1/32\sim1/64$ ), the data of total line number of LCD screen, from the line specified by display start line instruction, is displayed.

#### 12-5. Status Read

| RS | R/W | DB7  | DB6 | DB5    | DB4   | DB3 | DB2 | DB1 | DB0 |

|----|-----|------|-----|--------|-------|-----|-----|-----|-----|

| 0  | 0   | BUSY | 0   | ON/OFF | RESET | 0   | 0   | 0   | 0   |

BUSY

When BUSY is 1, the Chip is executing internal operation and no instructions are accepted.

When BUSY is 0, the Chip is ready to accept any instructions.

#### ■ ON/OFF

When ON/OFF is 1, the display is on.

When ON/OFF is 0, the display is off.

RESET

When RESET is 1, the system is being initialized.

In this condition is 0, no instructions except status read can be accepted.

When RESET is 0, initialized has finished and the system is in the usual operation condition

#### 12-6. Write Display data

| R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

Writes data (D0~D7) into the display data RAM.

After writing instruction, Y addressed is increased 1 automatically.

#### 12-7. Read Display data

| R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

Reads data (D0~D7) from the display data RAM.

After reading instruction, Y addressed is increased 1 automatically.

### **13. LCD MODULES HANDLING PRECAUTIONS**

- Please remove the protection foil of polarizer before using.

- The display panel is made of glass. Do not subject it to a mechanical shock by dropping it from a high place, etc.

- If the display panel is damaged and the liquid crystal substance inside it leaks out, do not get any in your mouth. If the substance come into contact with your skin or clothes promptly wash it off using soap and water.

- Do not apply excessive force to the display surface or the adjoining areas since this may cause the color tone to vary.

- The polarizer covering the display surface of the LCD module is soft and easily scratched. Handle this polarize carefully.

- To prevent destruction of the elements by static electricity, be careful to maintain an optimum work environment.

Be sure to ground the body when handling the LCD module.

- -Tools required for assembly, such as soldering irons, must be properly grounded.

-To reduce the amount of static electricity generated, do not conduct assembly and other work under dry conditions. -The LCD module is coated with a film to protect the display surface. Exercise care when peeling off this protective film since static electricity may be generated.

Storage precautions

When storing the LCD modules, avoid exposure to direct sunlight or to the light of fluorescent lamps. Keep the modules in bags designed to prevent static electricity charging under low temperature / normal humidity conditions (avoid high temperature / high humidity and low temperatures below 0°C). Whenever possible, the LCD modules should be stored in the same conditions in which they were shipped from our company.

### **14. OTHERS**

- Liquid crystals solidify at low temperature (below the storage temperature range) leading to defective orientation of liquid crystal or the generation of air bubbles (black or white). Air bubbles may also be generated if the module is subjected to a strong shock at a low temperature.

- If the LCD modules have been operating for a long time showing the same display patterns may remain on the screen as ghost images and a slight contrast irregularity may also appear. Abnormal operating status can be resumed to be normal condition by suspending use for some time. It should be noted that this phenomena does not adversely affect performance reliability.

- To minimize the performance degradation of the LCD modules resulting from caused by static electricity, etc. exercise care to avoid holding the following sections when handling the modules:

- Exposed area of the printed circuit board

- Terminal electrode sections