## DISPLAY Elektronik GmbH

## DATA SHEET

# 7,0" TFT MODULE

## **DEM 480234A TMH-PW-N**

**Product Specification**

Version: 2.0

06.09.2007

| REVISION | N HISTORY: |                                                                                   |            |             |

|----------|------------|-----------------------------------------------------------------------------------|------------|-------------|

| Revision | Date       | Description                                                                       | Written By | Approved By |

| 1.0      | 31-Aug2007 | New Release                                                                       | ХН         | JY          |

| 2.0      | 06-Sep2007 | Modify "Item 1.0 General Specification" Modify "Item 8.0 Backlight Specification" | XH         | MH          |

## **CONTENTS**

| 1.0  | GENERAL SPECIFICATION                  |

|------|----------------------------------------|

| 2.0  | OUTLINE DRAWING                        |

| 3.0  | INTERFACE PIN CONNECTION               |

| 4.0  | ABSOLUTE MAXIMUM RATIINGS              |

| 5.0  | ELECTRO-OPTICAL SPECIFICATION          |

| 6.0  | DC CHARACTERISTICS                     |

| 7.0  | BACKLIGHT SPECIFICATION                |

| 8.0  | STANDARD SPECIFICATION FOR RELIABILITY |

| 9.0  | QUALITY ASSURANCE                      |

| 10.0 | PRECAUTIONS FOR USING LCD MODULE       |

| 11.0 | LOT NUMBERING SYSTEM                   |

| 12.0 | PACKAGING STANDARD                     |

| 13.0 | RoHS COMPLIANT PRODUCT                 |

| 14.0 | LIMITED WARRANTY                       |

#### 1.0 GENERAL SPECIFICATION

| Item                   | Contents                           | Unit    |

|------------------------|------------------------------------|---------|

| LCD Type               | TFT-color transmissive LCD         | -       |

| Module outer dimension | $164.90 \times 100.00 \times 5.70$ | mm      |

| Active display area    | 154.08 × 86.58                     | mm      |

| Number of dots         | 480xRGB x 234                      | dots    |

| Pixel driving element  | a-SI TFT                           | -       |

| Pixel arrangement      | RGB-Stripe                         | -       |

| Pixel Size             | $0.107 \times 0.370$               | mm      |

| Viewing Direction      | 12                                 | O'clock |

| Backlight              | LED, White, Lightguide             | -       |

| Drive IC               | HX8226A+HX8615B (HIMAX)            | -       |

| Display colors         | Analog full color                  | -       |

| MPU interface          | Analog                             | -       |

| Operating temperature  | -20°C ~ 70°C                       | °C      |

| Storage temperature    | -30°C ~ 80°C                       | °C      |

| Weight                 | ~ 169                              | g       |

2.0

## **OUTLINE DRAWING** CONTACT SIDE LIGHT SHIELDING TAPE- $0.14\pm0.03$ $0.30\pm0.05$ STIFFENER-100.0±0.10 40.57±0.5 3.7 96.9 88.9±0.10(BZL) 86.58(A.A.) P0.5X25=12.50±0.05 52.47±0.5 $13.5\pm0.2$ $0.30\pm0.05$ DDTS: 480×RGB×234 56.00±0.10(BZL) $0.5\pm0.05$ 5.0±0.5-154.08(A.A.) 4.0±0.3--0.107 $90.0 \pm 5.0$ **→** 0.37 **→** 4.86--(30X10) 50.0 6.0H-25.0X03.1M

#### 3.0 INTERFACE PIN CONNECTION

| Pin No. | Symbol | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1       | GND    | Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 2       | VCC    | Power supply for digital circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 3       | VGL    | Negative power supply for X1~X240 outputs                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 4       | VGH    | Positive power supply for X1~X240 outputs.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 5       | STVD   | These two pins are the device start pulse input or output pin, the function of these two pins depends on the status of LR pin. When LR="L", STVD is enabled output and STVU is enabled input. When LR="H", STVD is enabled input and STVU is enabled output. Start pulse is read at the rising edge of CPV and a scan signal is output from the driver output pin. Start pulse goes up to high level at the 240 <sup>th</sup> falling edge of CPV and goes down to low |  |  |  |  |  |

| 6       | STVU   | level are the 241 <sup>st</sup> falling edge of CPV.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 7       | CKV    | This is the clock input for chip internal shift register. Data is shifted at each rising edge of this clock.                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 8       | U/D    | Shift up or down control,<br>U/D="H", up shift: STVD (input)~X1~X240~STVU (output).<br>U/D="L", down shift: STVU (input)~X240~X1~STVD (output)                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 9       | OEV    | Output off, active high. The driver outputs are disabled, output=VEE, when OEV is connected to high "1". Under this condition, the operation of registers will not be affected.                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 10      | VCOM   | Common electrode driving signal.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 11      | VCOM   | Common electrode driving signal.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 12      | L/R    | Select left or right shift, normally pulled high. L/R=H, STH1~QX1~QX2~QX240~STH2. L/R=L,STH2~QX240~QX239~QX1~STH1.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 13      | MOD    | Clock select signal on latching RGB signals.  MOD=0: Latching R, G, B signals to QAx,QBx,QCx, by the rising edge of CPH1,CPH2 and CPH3, normally pull low.  Mod=1: latching R,G,B signal by CPH1.                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 14      | OEH    | Enables outputs, QA1 to QC240, and the dual sample & hold circuit will be switched at the falling edge of OEH.                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 15      | STHL   | Input output switch of start pulse. Start pulse input pin and                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 16      | STHR   | cascade output pin is controlled by L/R input.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 17      | СРН3   | A clock pulse is simulated to CPH1.  When L/R=H, sequentially latches the input data, VC, at using the rising edge into embedded buffers from QC1 to QC240.  When L/R=L, latches the input data, VA to the buffers from QA240 to QA1.  When MOD=H, CQH3 must be connected to VDD or VSS.                                                                                                                                                                               |  |  |  |  |  |

| 18 | СРН2 | Clock signal for latching video signal, using the rising edge of this signal to sample and hold the input data sequentially, VB, into embedded buffers.  When L/R=H, the data are applied form QB1 to QB 240.  When L/R=L, the data are applied from QB240 to QB1.  When MOD=H,CPH2 must be connected to VDD or VSS.                                                                                                                                                 |  |  |  |

|----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 19 | СРН1 | Clock signal for latching video signals. When L/R=H, using the rising edge of this signal to samples and hold the input data, VA, into embedded buffers. The data are applied from QA1 to QA240 sequentially, then these data are output through output pins. When L/R=L, using the rising edge of this signal to sample and hold the input data, VC, into embedded buffers. The data are applied from QC240 to QC1, then these data are output through output pins. |  |  |  |

| 20 | VCC  | Power supply for digital circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 21 | GND  | Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 22 | VR   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 23 | VG   | Analog signal inputs for R,G,B data.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 24 | VB   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 25 | AVDD | Power supply for analog circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 26 | AVSS | Analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

#### 4.0 ABSOLUTE MAXIMUM RATINGS

| Item                      | Symbol   | Unit | Value            | Note |

|---------------------------|----------|------|------------------|------|

| Digital Power Supply      | Vcc      | V    | -0.3 to +7.0     |      |

| Analog power supply       | AVDD     | V    | -0.3 to +7.0     |      |

| Video input voltage       | VA,VB,VC | V    | -0.2 to AVDD+0.3 |      |

| Positive power supply     | VGH      | V    | 7 to VEE+40      |      |

| Negative power supply     | VEE      | V    | -20 to -5        |      |

| Input Voltage             | VI       | V    | -0.3 to VCC+0.3  |      |

| LSI Operating Temperature | Topr     | °C   | -10 to +70       |      |

| LSI Storage Temperature   | Tstg     | °C   | -30 to +80       |      |

#### **5.0 ELECTRO-OPTICAL CHARACTERISTICS**

| No | Item                             |       | Symbo 1          | Measur<br>Conditi                                              |              | Min.  | Тур.  | Max.  | Unit              | Note                 |

|----|----------------------------------|-------|------------------|----------------------------------------------------------------|--------------|-------|-------|-------|-------------------|----------------------|

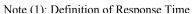

| 1  | Response                         | Rise  | Tr               | $ \phi = 0_{o} \\ \theta = 0_{o} $                             | 25 °C        | -     | 15    | 30    | ms                | N. (1)               |

| 1  | Time                             | Fall  | Tf               | $ \begin{aligned} \phi &= 0_o \\ \theta &= 0_o \end{aligned} $ | 25 °C        | -     | 35    | 50    | ms                | Note (1)             |

|    |                                  |       | $\theta_R$       | $\phi = 0_{\rm o}$                                             | 25 °C        | -     | 45    | -     |                   |                      |

| 2  | Viewing Angle                    | e     | θL               | $\phi = 180^{\circ}$                                           | 25 °C        | -     | 45    | -     | Deg               | Note (3)             |

| 2  | $(CR \ge 10)$                    |       | θυ               | $\phi = 90^{\circ}$                                            | 25 °C        | -     | 35    | -     | Deg               | Note (3)             |

|    |                                  |       | θD               | $\phi = 270^{\circ}$                                           | 25 °C        | -     | 10    | -     |                   |                      |

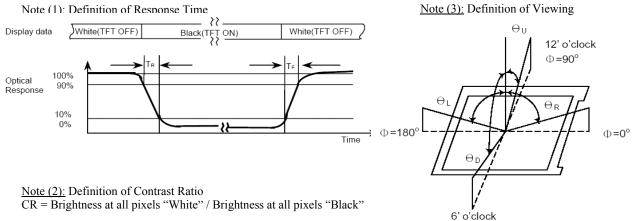

| 3  | Contrast Ratio                   | •     | CR               | -                                                              | 25 °C        | 150   | 250   | -     | -                 | Note (2)             |

| 4  | Luminance of white(Center point) |       | L                | -                                                              | 25 °C        | 200   | 250   |       | Cd/m <sup>2</sup> | Note (5)             |

| 5  | Transmissive rate                |       | Т%               |                                                                |              | _     | 8.6   | _     | %                 |                      |

|    |                                  |       | $X_R$            |                                                                |              | 0.585 | 0.615 | 0.645 | -                 |                      |

|    |                                  | Red   | Y <sub>R</sub>   |                                                                |              | 0.314 | 0.344 | 0.374 | -                 |                      |

|    |                                  |       | $X_{G}$          | Viewing n                                                      | ormal        | 0.277 | 0.307 | 0.337 | -                 | <b>N</b> I ( (4)     |

| 6  | 6 Chromaticity                   | Green | $Y_{G}$          | angle θx                                                       | <b>≤</b> =0° | 0.533 | 0.563 | 0.593 | -                 | Note (4)<br>NTSC=50% |

|    |                                  | DI    | X <sub>B</sub>   | θy=0                                                           | 0            | 0.103 | 0.133 | 0.163 | -                 | N1SC=50%             |

|    |                                  | Blue  | Y <sub>B</sub>   |                                                                |              | 0.120 | 0.150 | 0.180 | -                 |                      |

|    |                                  | White | $X_{\mathrm{W}}$ |                                                                |              | 0.279 | 0.309 | 0.339 | -                 |                      |

|    |                                  | White | Y <sub>W</sub>   |                                                                |              | 0.320 | 0.350 | 0.380 | -                 |                      |

Note (4): Measured at center point vertically with backlight on.

Note(5): After stabilizing and leaving the panel alone at a given temperature for 30 min, the measurement should be executed .Measurement should be executed in a stable, windless, and dark room. 30 min after lighting the back-light. This should be measured in the center of screen.

Φ=270°

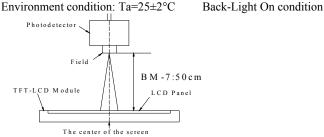

#### 6.0 DC CHARACTERISTICS

(DVDD=2.5 to 5.5V, AVDD=3.0 to 5.5V, T<sub>OPR</sub>=25°C)

| Parameter                      | Symbol          | Min.      | Тур.     | Max.    | Unit | Conditions                                                    |

|--------------------------------|-----------------|-----------|----------|---------|------|---------------------------------------------------------------|

| Supply voltage                 | AVDD            | 3         |          | 5.5     | V    | 0) // -                                                       |

| Supply voltage                 | DVDD            | 2.5       | - []     | 5.5     | - V  | _                                                             |

| Low level input voltage        | V <sub>IL</sub> | 0         |          | 0.3DVDD | ~    | CPH1~CPH3, OE,<br>L/R, STH1, STH2,<br>Q1H, Q2H, MOD,<br>CHNSL |

| High level input voltage       | V <sub>IH</sub> | 0.7DVDD   |          | DVDD    | V    | CPH1~CPH3, OE,<br>L/R, STH1, STH2,<br>Q1H, Q2H, MOD,<br>CHNSL |

| Input leakage current          | I <sub>IN</sub> | -C        | ) -      | ±1      | μА   | CPH1~CPH3, OE,<br>STH1, STH2, Q1H,<br>Q2H, L/R, MOD,<br>CHNSL |

| High level output voltage      | V <sub>он</sub> | DVDD -0.4 | -        | DVDD    | V    | STH1, STH2,<br>I <sub>OH</sub> =-400µA                        |

| Low level output voltage       | Vol             | 0         | -        | 0.4     | V    | STH1, STH2,<br>I <sub>OL</sub> =400µA                         |

| Voltage deviation of<br>output | V <sub>VD</sub> | -         | ±20      | -       | m∨   | QA1 to QC240,<br>V <sub>IN</sub> =0.1~4.9V                    |

| DC offset                      | Vos             | -         | -        | ±20     | mV   | Vx to QAx~QCx                                                 |

| Dynamic range of<br>output     | $V_{DR}$        | AVDD -0.4 | AVDD-0.2 | -       | ~    | QA1 to QC240,<br>0.1 to 4.9V<br>(AVDD =5V)                    |

| Output current                 | I <sub>OH</sub> | 20        | 40       | -       | μΑ   | QA1 to QC240,<br>(AVDD =5V)<br>V <sub>0</sub> =4.9V vs. 4.0V  |

| Output current                 | I <sub>OL</sub> | 20        | 40       | -       | μА   | QA1 to QC240,<br>(AV <sub>DD</sub> =5V)<br>Vo=0.1V vs. 1.0V   |

(Please also refer to datasheet of TFT driver)

#### 7.0 BACKLIGHT SPECIFICATION

| Item                         | Symbol | Min. | Тур. | Max.     | Unit              | Conditions   |

|------------------------------|--------|------|------|----------|-------------------|--------------|

| Forward voltage              | Vf     | -    | 9.6  | -        | V                 | If=150mA     |

| Reverse current              | Ir     | 0    | 50   | -        | μΑ                | T=25°C       |

| Chromaticity                 | X      | 0.28 | -    | 0.32     | -                 |              |

| coordinates                  | Y      | 0.28 | -    | 0.33     | -                 |              |

| Luminance                    | Lv     | 2200 | 2500 | 3000     | cd/m <sup>2</sup> |              |

| Forward current              | If     | -    | 150  | -        | mA                | Vf=9.6V      |

| Uniformity                   | Δ      | 75   | 80   | -        | %                 | Min/max*100% |

| Half-Brightness<br>Life Time |        |      | 1    | 30000hou | urs               |              |

#### 8.0 STANDARD SPECIFICATION FOR RELIABILITY

#### 8.1 Standard specification of Reliability Test

| No | Test Item                                | Content of Test                                                                                                         |                           | <b>Test Condition</b>    | n Applicable<br>Standard       |  |

|----|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------|--------------------------------|--|

| 1  | High temperature storage                 | Endurance test applying the high storage temperature for a long time.                                                   | ge                        | 80+/-3 °C<br>240 hrs     |                                |  |

| 2  | Low temperature storage                  | Endurance test applying the low storag temperature for a long time.                                                     | e                         | -30+/-3 °C<br>240 hrs    |                                |  |

| 3  | High temperature operation               | Endurance test applying the electric str (Voltage & Current) and the thermal st the element for a long time.            |                           | 70+/-3 °C<br>240 hrs     |                                |  |

| 4  | Low temperature operation                | Endurance test applying the electric str under low temperature for a long time.                                         | ess                       | -10+/-3 °C<br>240 hrs    |                                |  |

| 5  | High temperature /<br>Humidity operation | Endurance test applying the electric str (Voltage & Current) and temperature / humidity stress to the element for a lon |                           | 40 °C, 90 %RH<br>120 hrs | MIL-202E-<br>103B<br>JIS-C5023 |  |

| 6  | Temperature cycle                        | Endurance test applying the low and hi temperature cycle.  -30°C \( 30\text{min.} \( \) \( \) \( \) \( \) \( \) 1 cycle | -30°C / 80°C<br>10 cycles |                          |                                |  |

|    | Mechanical Test                          |                                                                                                                         |                           |                          |                                |  |

| 7  | Drop Test                                | Endurance test applying the drop during transportation.                                                                 | 100cm free des, 1 corner, |                          |                                |  |

#### Remarks:

#### 8.2 Failure Judgment Criteria

After the reliability tests above, test sample shall be let return to room temperature and humidity for at least 4 hours before final tests are carried out.

| Criterion Item            | Failure Judgment Criteria       |

|---------------------------|---------------------------------|

| Electrical characteristic | Electrical short and open.      |

| Mechanical characteristic | Out of mechanical specification |

| Optical characteristic    | Out of the Appearance Standard  |

For operation test, above specification is applicable when test pattern is changing during entire operation test.

<sup>14</sup> Inspections after reliability tests are performed when the display temperature resumes back to room temperature.

<sup>15</sup> It is a normal characteristic that some display abnormality can be seen during reliability test. If the display abnormality can resume back to normal condition at room temperature within 24hours, there is no permanent destruction over the display. The display still possesses its functionality after reliability tests.

### 9.0 QUALITY ASSURANCE

#### 9.1 Acceptable Quality Level (AQL)

Each lot should satisfy the quality level defined as follows:

a) Inspection method: MIL-STD-105E Level II normal one time sampling

b) AQL level

| Category | AQL   | Definition                                                         |  |  |

|----------|-------|--------------------------------------------------------------------|--|--|

| Major    | 0.25% | Functional defective as product                                    |  |  |

| Minor    | 1.00% | Satisfy all functions as product but not satisfy cosmetic standard |  |  |

#### 9.2 Cosmetic Screening Criteria

| No | Defect                                         | Judgment Criteria                                                                                        |                                                             |                                                          |       |  |

|----|------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------|-------|--|

| 1  | Spots/Dust<br>/Bubble<br>(Round type)          | Size, d (mm)Acceptable quantity in active area $d \le 0.15$ Disregard $0.15 < d \le 0.20$ 3 $d > 0.20$ 0 |                                                             | Disregard 3                                              | Minor |  |

| 2  | Dust/Scratches/<br>Black streak<br>(Line type) | $Width, W (mm)$ $W \le 0.02$ $W \le 0.03$ $W \le 0.05$ $W > 0.05$                                        | Length, L (mm)  Disregard $L \le 1.0$ $L \le 2.0$ Disregard | Acceptable quantity in active area Disregard Disregard 3 | Minor |  |

| 3  | Allowable density                              | Above defects should be separated more than 5mm each other.                                              |                                                             |                                                          |       |  |

| 4  | Rainbow                                        | Obvious uneven color (rainbow) shall not be noticeable.                                                  |                                                             |                                                          |       |  |

| 5  | Display condition                              | Dim display on the patterns, extra pattern and short circuit are not acceptable.                         |                                                             |                                                          |       |  |

| 6  | No display or missing display                  | The patterns of display shall light up as required. No display or missing display are not acceptable.    |                                                             |                                                          |       |  |

Note: d = (long length + short length) / 2

#### 10.0 PRECAUTIONS FOR USING LCD MODULE

#### **Handing Precautions**

- Observe the following when soldering lead wire, connector cable and etc. to the LCD module.

- Soldering iron temperature: 300 ~ 350°C.

- Soldering time:  $\leq 3$  sec.

- Solder: eutectic solder.

- Above is a recommended approach. Due to different solder composition and processing method, it is recommended that customer to study and fine tuning their soldering process parameters accordingly.

- If soldering flux is used, be sure to remove any remaining flux after finishing to soldering operation. (This does not apply in the case of a non-halogen type of flux.) It is recommended that you protect the LCD surface with a cover during soldering to prevent any damage due to flux spatters.

#### **Precautions for Operation**

- Viewing angle varies with the change of liquid crystal driving voltage (V<sub>O</sub>). Adjust V<sub>O</sub> to show the best contrast.

- Driving the LCD in the voltage above the limit shortens its lifetime.

- Response time is greatly delayed at temperature below the operating temperature range. However, it will recover when it returns to the specified temperature range.

- If the display area is pushed hard during operation, the display will become abnormal. However, it will return to normal if it is turned off and then back on.

- When turning the power on, input each signal after the positive/negative voltage becomes stable.

#### Storage

- When storing LCDs as spares for some years, the following precautions are necessary.

- Store them in a sealed polyethylene bag. If properly sealed, there is no need for desiccant.

- Store them in a dark place. Do not expose to sunlight or fluorescent light, keep the temperature between 0°C and 35°C.

- Environmental conditions:

- Do not leave them for more than 168hrs. at 60°C.

- Should not be left for more than 48hrs, at -20°C.

#### **Safety**

- It is recommended to crush damaged or unnecessary LCD into pieces and wash them off with solvents such as acetone and ethanol, which should later be burned.

- If any liquid leaks out of a damaged glass cell and comes in contact with the hands, wash off thoroughly with soap and water.

#### 11.0 LOT NUMBERING SYSTEM

#### 11.1 Definition of Lot Number

One lot means the delivery date and times to customer at one time.

## $\frac{\mathbf{YYMMDD}}{(1)} \frac{\mathbf{XXX}}{(2)}$

- (1) Manufacturing date (COG bonding) (YY: Year, MM: Month, DD: Day)

- (2) Serial number starts from A01,A02.....A99,B01,B02......

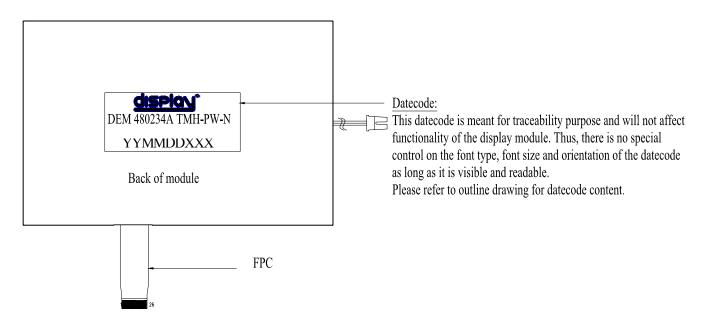

#### 11.2 Location of datecode number

#### 12.0 ROHS COMPLIANT PRODUCT

#### Standard of specific chemical substance

| 1. | Cadmium and Cadmium Compounds          | Less than 100ppm  |

|----|----------------------------------------|-------------------|

| 2. | Hexavalent Chromium Compounds          | Less than 1000ppm |

| 3. | Lead and Lead Compounds                | Less than 1000ppm |

| 4. | Mercury and Mercury Compounds          | Less than 1000ppm |

| 5. | Polybrominated Biphenyls (PBBs)        | Less than 1000ppm |

| 6. | Polybrominated Diphenyl ethers (PBDEs) | Less than 1000ppm |

#### 13.0 LIMITED WARRANTY

Please inspect the LCD modules within one month after your receipt. Unless agreed between DISPLAY and customer, DISPLAY will replace or repair any of its LCD modules, which are found to be functionally defective when inspected in accordance with DISPLAY LCD/LCM acceptance standards (copies available upon request) for a period of one year from date of shipments. Cosmetic/visual defects must be returned to DISPLAY within 90 days of shipment. Confirmation of such date shall be based on freight documents. The warranty liability of DISPLAY limited to repair and/or replacement on the terms set forth above. DISPLAY will not be responsible for any subsequent or consequential events.