### International ICR Rectifier

### HEXFET<sup>®</sup> Power MOSFET

- Isolated Package

- High Voltage Isolation= 2.5KVRMS (5)

- Sink to Lead Creepage Dist.= 4.8mm

- Dynamic dv/dt Rating

- I ow Thermal Resistance

# **IRFI720G**

$$V_{DSS} = 400V$$

$R_{DS(on)} = 1.8\Omega$

$I_D = 2.6A$

#### Description

Third Generation HEXFETs from International Rectifier provide the designer with the best combination of fast switching, ruggedized device design, low on-resistance and cost-effectiveness.

The TO-220 Fullpak eliminates the need for additional insulating hardware in commercial-industrial applications. The moulding compound used provides a high isolation capability and a low thermal resistance between the tab and external heatsink. This isolation is equivalent to using a 100 micron mica barrier with standard TO-220 product. The Fullpak is mounted to a heatsink using a single clip or by a single screw fixing.

#### Absolute Maximum Ratings

|                                        | Parameter                             | Max.                  | Units |

|----------------------------------------|---------------------------------------|-----------------------|-------|

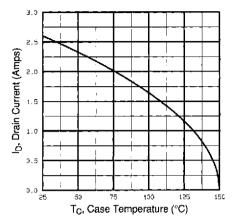

| lp@Tc≈25°C                             | Continuous Drain Current, Vos @ 10 V  | 2.6                   |       |

| lp @ Tc = 100°C                        | Continuous Drain Current, VGS @ 10 V  | 1.7                   | A     |

| 1DM                                    | Pulsed Drain Current (i)              | 10                    | 1     |

| P <sub>D</sub> @ T <sub>C</sub> = 25°C | Power Dissipation                     | 30                    | W     |

|                                        | Linear Derating Factor                | 0.24                  | W/ºC  |

| V <sub>GS</sub>                        | Gate-to-Source Voltage                | ±20                   | τīν i |

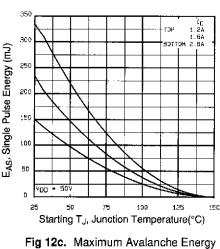

| EAS                                    | Single Pulse Avalanche Energy @       | 150                   | mJ    |

| lar                                    | Avalanche Current @                   | 2.6                   | Â     |

| Еля                                    | Repetitive Avalanche Energy ①         | 3.0                   | mJ    |

| dv/dt                                  | Peak Diode Recovery dv/dt ③           | 4.0                   | V/ns  |

| T,                                     | Operating Junction and                | -55 to +150           |       |

| TSTG                                   | Storage Temperature Range             |                       | °C    |

|                                        | Soldering Temperature, for 10 seconds | 300 (1.6mm from case) |       |

|                                        | Mounting Torque, 6-32 or M3 screw     | 10 lbf•in (1.1 N•m)   |       |

#### **Thermal Resistance**

|      | Parameter           | Min. | Тур. | Max. | Units |

|------|---------------------|------|------|------|-------|

| Reuc | Junction-to-Case    | —    | —    | 4.1  | ∘c/w  |

| Rwa  | Junction-to-Ambient | —    |      | 65   |       |

Document Number: 90189

www.vishay.com 629

#### Electrical Characteristics @ T<sub>J</sub> = 25°C (unless otherwise specified)

|                                        | Parameter                            | Min, | Тур. | Max. | Units | Test Conditions                                           |  |

|----------------------------------------|--------------------------------------|------|------|------|-------|-----------------------------------------------------------|--|

| V <sub>(BR)DSS</sub>                   | Drain-to-Source Breakdown Voltage    | 400  | _    | _    | V     | V <sub>GS</sub> =0V, I <sub>D</sub> = 250μA               |  |

| ΔV <sub>(BR)DSS</sub> /AT <sub>J</sub> | Breakdown Voltage Temp. Coefficient  | -    | 0.51 | _    | V/ºC  | Reference to 25°C, Ip= 1mA                                |  |

| RDS(on)                                | Static Drain-to-Source On-Resistance | _    | . —  | 1.8  | Ω     | V <sub>GS</sub> =10V, I <sub>D</sub> =1.6A ⊛              |  |

| VGS(th)                                | Gate Threshold Voltage               | 2.0  | -    | 4.0  | ٧     | V <sub>DS</sub> =V <sub>GS</sub> , I <sub>D</sub> = 250μA |  |

| <b>g</b> is                            | Forward Transconductance             | 1.5  | -    |      | S     | V <sub>DS</sub> =50V, I <sub>D</sub> =1.6A ④              |  |

| IDSS                                   | Drain-to-Source Leakage Current      | ļ    | —    | 25   |       | V <sub>DS</sub> =400V, V <sub>GS</sub> =0V                |  |

| 1055                                   | Diam-to-bouice Leakage outrent       |      |      | 250  | μA    | VDS=320V, VGS=0V, TJ=125°C                                |  |

| less                                   | Gate-to-Source Forward Leakage       | ]    | —    | 100  | nA    | V <sub>GS</sub> =20V                                      |  |

| 665                                    | Gate-to-Source Reverse Leakage       |      |      | -100 | Ĩ     | V <sub>GE</sub> =-20V                                     |  |

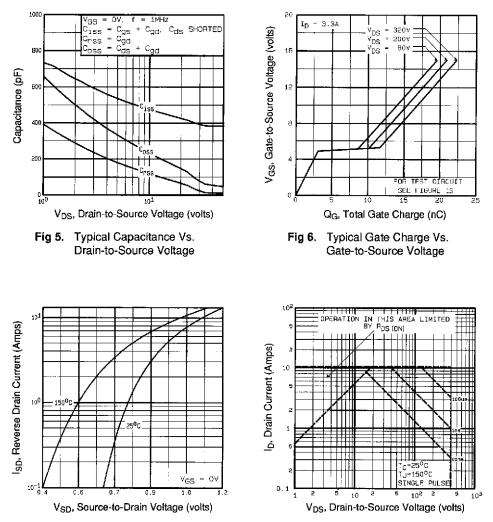

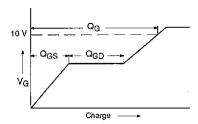

| Qg                                     | Total Gate Charge                    |      | —    | 20   |       | 1 <sub>D</sub> =3.3A                                      |  |

| Q <sub>gs</sub>                        | Gate-to-Source Charge                |      | —    | 3.3  | nC    | V <sub>DS</sub> =320V                                     |  |

| Q <sub>gd</sub>                        | Gate-to-Drain ("Miller") Charge      | _    |      | 11   |       | V <sub>GS</sub> =10V See Fig. 6 and 13 ④                  |  |

| td(on)                                 | Tum-On Delay Time                    |      | 10   | —    |       | V <sub>DD</sub> =200V                                     |  |

| tr                                     | Rise Time                            | —    | 14   | —    | ns    | ID=3.3A                                                   |  |

| td(off)                                | Tum-Off Delay Time                   |      | 30   | —    |       | R <sub>G</sub> =18Ω                                       |  |

| tf                                     | Fall Time                            | —    | 13   | —    |       | R <sub>D</sub> =56Ω See Figure 10 ⊕                       |  |

| LD                                     | Internal Drain Inductance            | -    | 4.5  |      |       | Between lead,<br>6 mm (0.25in.)                           |  |

| Ls                                     | Internal Source Inductance           |      | 7.5  |      | nH    | from package<br>and center of<br>die contact              |  |

| Ciss                                   | Input Capacitance                    |      | 410  | _    |       | V <sub>GS</sub> =0V                                       |  |

| Coss                                   | Output Capacitance                   | —    | 120  | l    | рF    | V <sub>DS</sub> = 25V                                     |  |

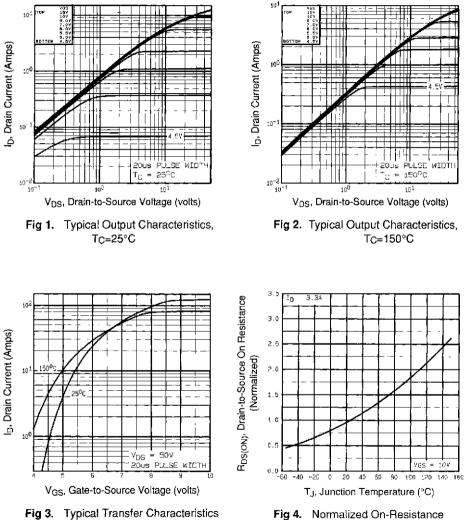

| Crss                                   | Reverse Transfer Capacitance         | _    | 47   | ĺ    |       | f=1.0MHz See Figure 5                                     |  |

| С                                      | Drain to Sink Capacitance            | _    | 12   | _    | рF    | <i>f</i> =1.0MHz                                          |  |

#### Source-Drain Ratings and Characteristics

|                 | Parameter                                 | Min.                                                                         | Typ. | Max. | Units | Test Conditions                         |

|-----------------|-------------------------------------------|------------------------------------------------------------------------------|------|------|-------|-----------------------------------------|

| ls              | Continuous Source Current<br>(Body Diode) | _                                                                            |      | 2.6  |       | MOSFET symbol showing the               |

| Ism             | Pulsed Source Current<br>(Body Diode) ①   | -                                                                            | -    | 10   | A     | integral reverse<br>p-n junction diode. |

| Vsn             | Diode Forward Voltage                     | _                                                                            | _    | 1.6  | V     | TJ=25°C, IS=2.6A, VGS=0V @              |

| t <sub>rr</sub> | Reverse Recovery Time                     | _                                                                            | 300  | 600  | ns    | Tj=25°C, I⊧=3.3A                        |

| Qrr             | Reverse Recovery Charge                   | _                                                                            | 1.5  | 3.0  | μC    | di/dt≕100A/µs ⊛                         |

| t <sub>on</sub> | Forward Turn-On Time                      | Intrinsic turn-on time is neglegible (turn-on is dominated by $L_{S}+L_{D})$ |      |      |       |                                         |

#### Notes:

- ③ Repetitive rating; pulse width limited by max, junction temperature (See Figure 11)

- (3) I<sub>SD</sub>≤3.3A, di/dt≤65A/μs, V<sub>DD</sub>≤V<sub>(BR)DSS</sub>, (5) t=60s, *f*=60Hz T<sub>J</sub>≤150°C

- ② V<sub>DD</sub>=50V, starting T<sub>J</sub>=25°C, L=38mH R<sub>G</sub>=25Ω, I<sub>AS</sub>=2.6A (See Figure 12)

- $\circledast$  Pulse width < 300  $\mu s;$  duty cycle <2%.

DATA Sheets

Vs. Temperature

Document Number: 90189

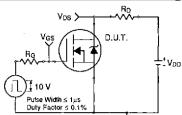

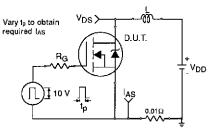

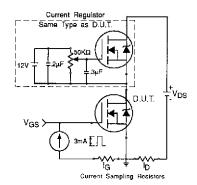

Fig 10a. Switching Time Test Circuit

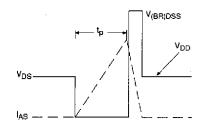

Fig 10b. Switching Time Waveforms

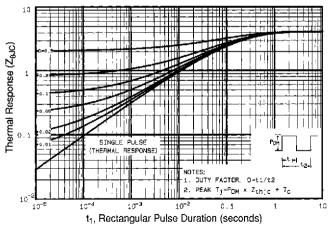

Fig 11. Maximum Effective Transient Thermal Impedance, Junction-to-Case

DATA Sheets

### <u>IRFI720G</u>

Fig 12a. Unclamped Inductive Test Circuit

Fig 12b. Unclamped Inductive Waveforms

Fig 13a. Basic Gate Charge Waveform

Appendix A: Figure 14, Peak Diode Recovery dv/dt Test Circuit - See page 1505

Appendix B: Package Outline Mechanical Drawing - See page 1510

Appendix C: Part Marking Information – See page 1517

Vs. Drain Current

Fig 13b. Gate Charge Test Circuit

Vishay

## Notice

The products described herein were acquired by Vishay Intertechnology, Inc., as part of its acquisition of International Rectifier's Power Control Systems (PCS) business, which closed in April 2007. Specifications of the products displayed herein are pending review by Vishay and are subject to the terms and conditions shown below.

Specifications of the products displayed herein are subject to change without notice. Vishay Intertechnology, Inc., or anyone on its behalf, assumes no responsibility or liability for any errors or inaccuracies.

Information contained herein is intended to provide a product description only. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Vishay's terms and conditions of sale for such products, Vishay assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of Vishay products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications. Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Vishay for any damages resulting from such improper use or sale.

International Rectifier<sup>®</sup>, IR<sup>®</sup>, the IR logo, HEXFET<sup>®</sup>, HEXSense<sup>®</sup>, HEXDIP<sup>®</sup>, DOL<sup>®</sup>, INTERO<sup>®</sup>, and POWIRTRAIN<sup>®</sup> are registered trademarks of International Rectifier Corporation in the U.S. and other countries. All other product names noted herein may be trademarks of their respective owners.