Suites 2202-7, 22/F, Tower 6, The Gateway,<br/>9 Canton Road, Tsimshatsui,<br/>Kowloon, Hong Kong<br/>Tel (852) 2123 3289WT65F4<br/>USB μC<br/>Flash me<br/>ADCFax (852) 2123 3393<br/>E-mail: <a href="mailto:sales@jesstech.com">sales@jesstech.com</a>HomePage: http://www.jesstech.com

WT65F4 USB μC with 8KB ISP Flash memory & 12bit ADC

# WT65F4

USB uC with 8KB ISP Flash Memory 12-bit A/D Converter

# **Data Sheet**

REV.1.00 Nov.18, 2001

1

The information in this document is subject to change without notice.

Suites 2202-7, 22/F, Tower 6, The Gateway,<br/>9 Canton Road, Tsimshatsui,<br/>Kowloon, Hong Kong<br/>Tel (852) 2123 3289WT65F4<br/>USB μC<br/>Flash me<br/>ADCFax (852) 2123 3393<br/>E-mail: <a href="mailto:sales@jesstech.com">sales@jesstech.com</a>HomePage: http://www.jesstech.com

WT65F4 USB µC with 8KB ISP Flash memory & 12bit ADC

# **Table of Content**

| GENERAL DESCRIPTION                            | 1                   |

|------------------------------------------------|---------------------|

| FEATURES                                       | 1                   |

| PACKAGE INFORMATION                            | 2                   |

| PIN ASSIGNMENT AND DESCRIPTION                 | 3                   |

| PIN CONFIGURATION                              | 5                   |

| FUNCTION DESCRIPTION                           | 7                   |

| WT65F4 USB MODULE                              | 7                   |

| MICROCONTROLLER                                |                     |

| ANALOG TO DIGITAL CONVERTER ( ADC )            | 11                  |

| PULSE WIDTH MODULATION( PWM )                  | 13                  |

| ADPCM PUSH-PULL D/A                            | 13                  |

| WT65F4 ADDRESS SPACE MAPPING                   | 14                  |

| WT65F4 SPECIAL FUNCTION REGISTER ADDRESS SPACE | 14                  |

| EXTERNAL FUNCTION REGISTER ADDRESS SPACE       | 16                  |

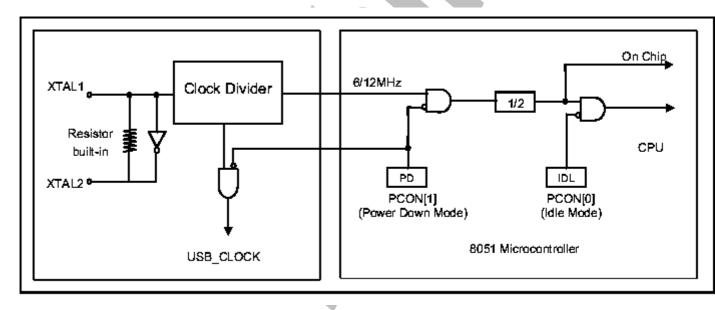

| CLOCK UNIT                                     |                     |

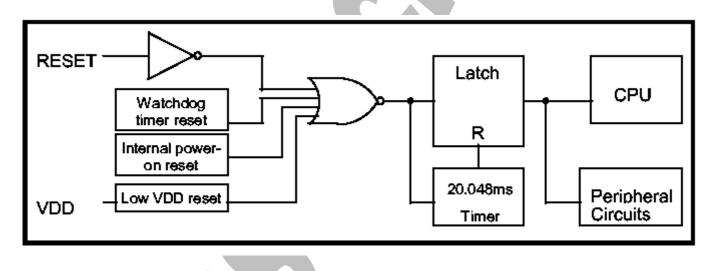

| RESET                                          | 19                  |

| POWERDOWN MODE AND IDLE MODE                   | 19                  |

| INTERRUPT                                      |                     |

|                                                |                     |

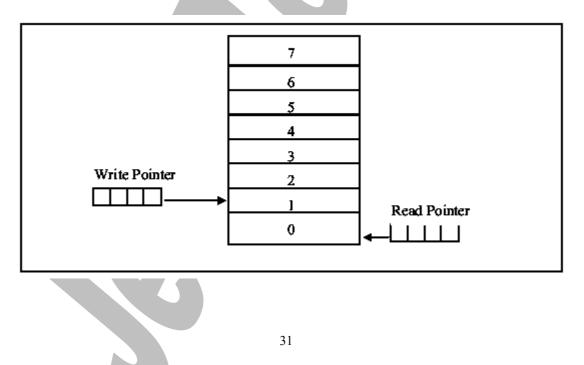

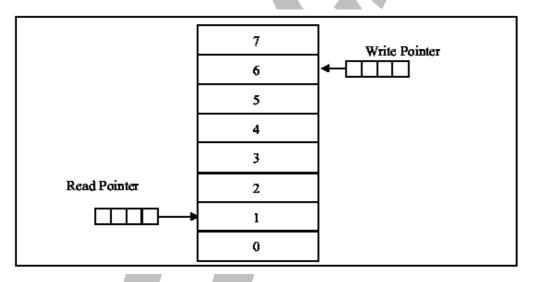

| TRANSMIT FIFOS                                 | 22                  |

|                                                |                     |

| TRANSMIT DATA SET MANAGEMENT                   | 23                  |

| TRANSMIT FIFO REGISTERS                        |                     |

| RECEIVE FIFOS                                  | 24                  |

| RECEIVE FIFO FEATURES                          | 24                  |

| RECEIVE DATA SET MANAGEMENT                    |                     |

|                                                |                     |

| SETUP TOKEN RECEIVE FIFO HANDLING              | 27                  |

| SUSPEND AND RESUME                             |                     |

| ISP MODE                                       | 29                  |

| ICE MODE                                       |                     |

| NORMAL DOWNLOAD MODE                           | 29                  |

| EXTERRNAL FUNCTION REGISTERS                   |                     |

| TRAGERT AC AND DC SPECIFICATION                | 66                  |

|                                                | PACKAGE INFORMATION |

USB µC with 8KB ISP F'ash memory & 12bit

# **Index of Figures**

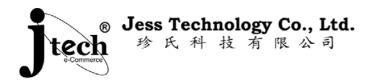

| Figure 1. WT65F4 40-pin DIP & 28-pin SOP / DIP package       | 5  |

|--------------------------------------------------------------|----|

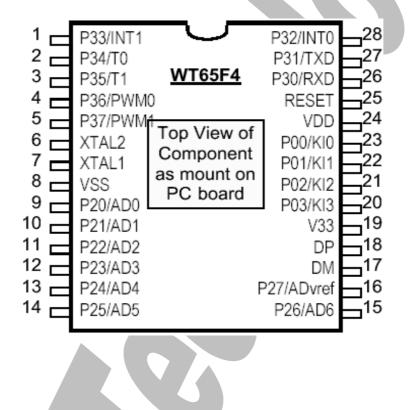

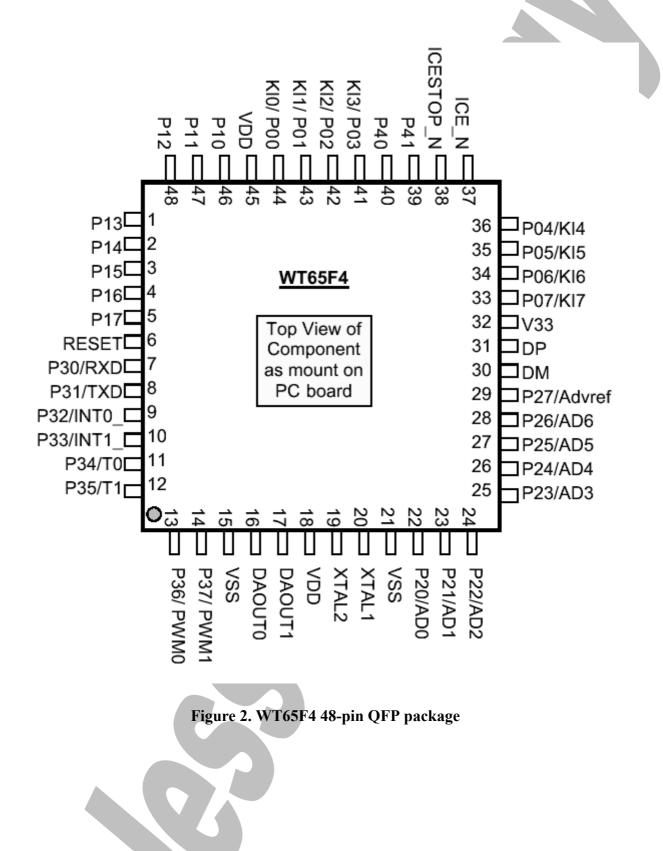

| Figure 2. WT65F4 48-pin QFP package                          | 6  |

| Figure 3. WT65F4 4General Block Diagram                      | 7  |

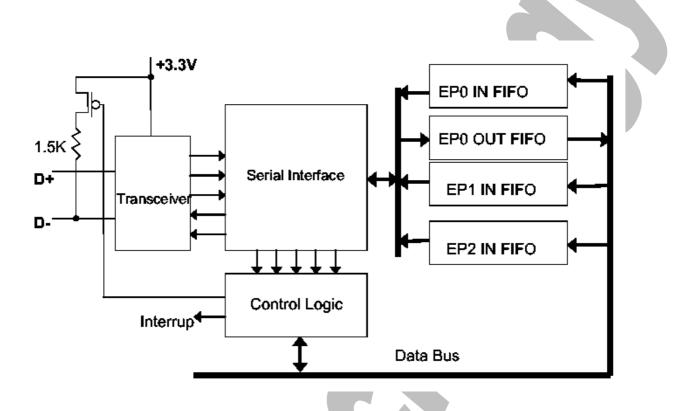

| Figure 4. USB Interface Block Diagram                        | 9  |

| Figure 5. Memory mapping of Flash ROM, boot ROM, and ICE ROM | 11 |

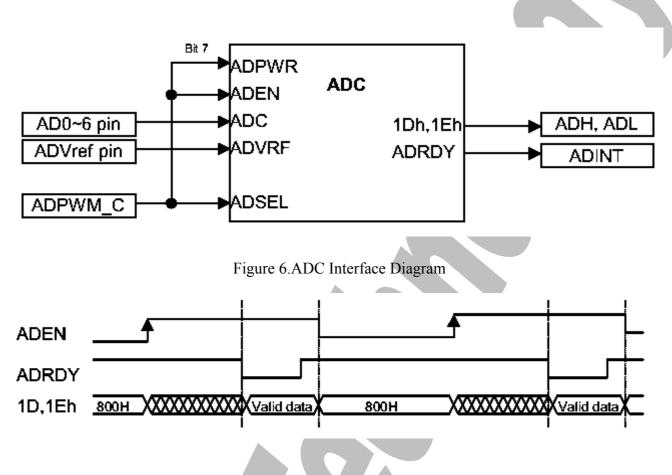

| Figure 6. ADC Interface Diagram                              | 12 |

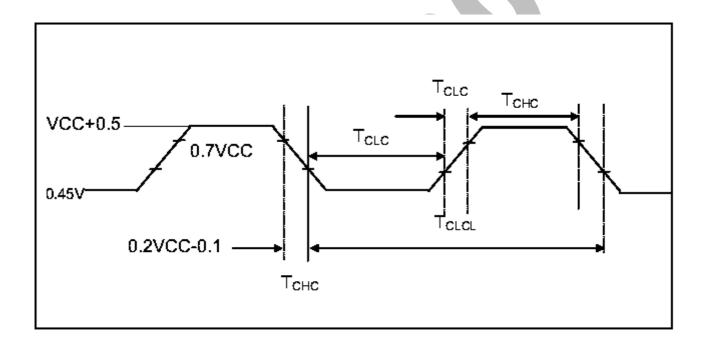

| Figure 7. ADC Timing Diagram                                 | 12 |

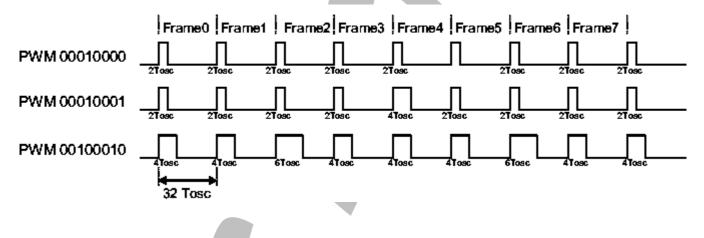

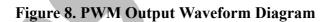

| Figure 8. PWM Output Waveform Diagram                        | 13 |

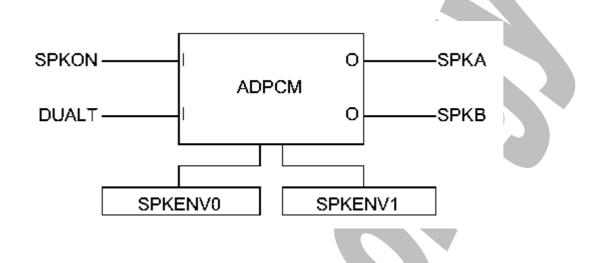

| Figure 9. ADPCM block diagram                                | 14 |

| Figure 10. Clock circuit when USB function is used           | 18 |

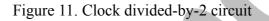

| Figure 11. Clock divided-by-2 circuit                        | 19 |

| Figure 12. Reset Signals                                     | 19 |

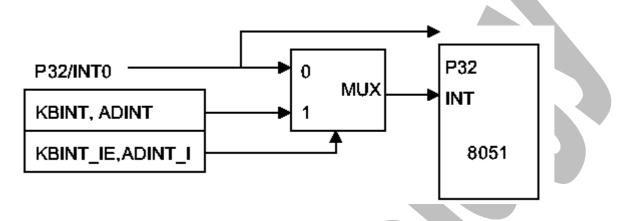

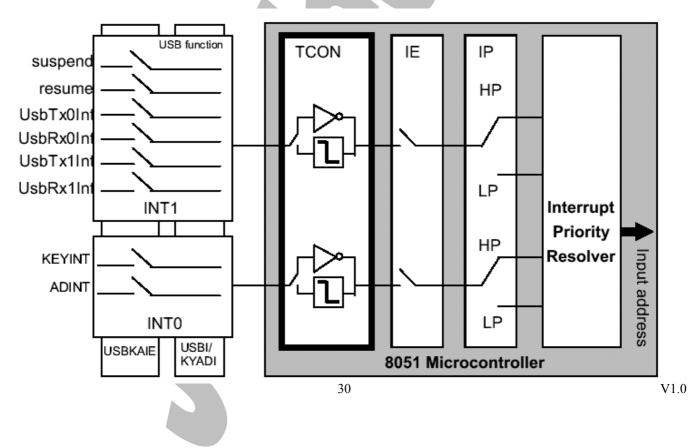

| Figure 13. Block Diagram of INT0                             | 21 |

| Figure 14. WT65F4 interrupt circuit                          | 21 |

| Figure 15. Transmit FIFO outline                             | 22 |

| Figure 16. Receive FIFO Outline                              | 25 |

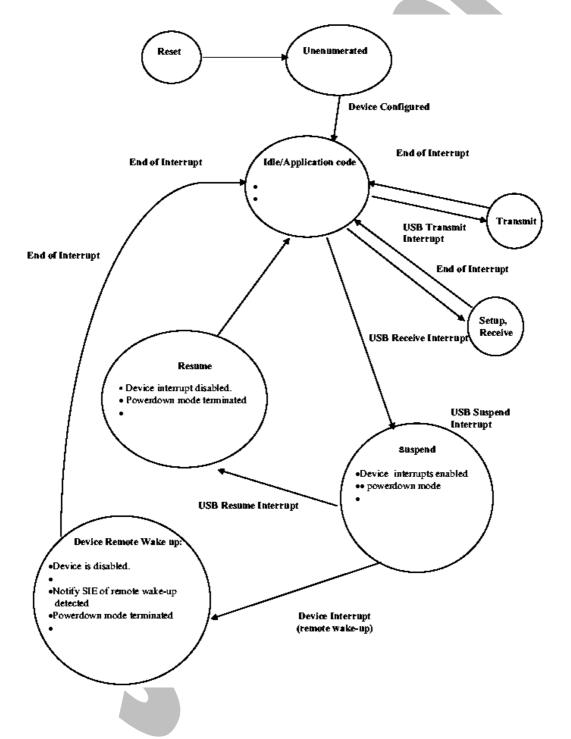

| Figure 17. Suspend and Resume State Diagram                  | 28 |

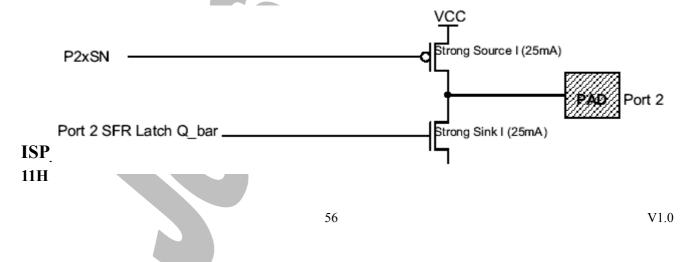

| Figure 18. Port 2 circuit diagram.                           | 47 |

| Figure 19. External Clock Drive Waveform                     | 67 |

Suites 2202-7, 22/F, Tower 6, The Gateway, WT65F4

9 Canton Road, Tsimshatsui,

Kowloon, Hong Kong

Tel (852) 2123 3289

Fax (852) 2123 3393

E-mail: sales@jesstech.com

HomePage: http://www.jesstech.com

USB µC with 8KB ISP F'ash memory & 12bit

# **Index of Tables**

| Table 1. WT65F4 Package Types                                              |    |

|----------------------------------------------------------------------------|----|

| Table 2. Pin Descriptions                                                  | 3  |

| Table 3. ADC Interface Description                                         |    |

| Table 4. Addressing mapping                                                | 14 |

| Table 5. WT65F4 Special Function Register (SFR) layout                     |    |

| Table 6. External Function Register ( XFR ) layout                         |    |

| Table 7. Internal clock generation map                                     |    |

| Table 8. Writing to the Byte Count Register                                |    |

| Table 9. Truth table for transmit FIFO management                          |    |

| Table 10. Status of the receive FIFO data set                              | 26 |

| Table 11. Truth table for receive FIFO management                          | 26 |

| Table 12. Function Address Register (FADDR, 00H )                          |    |

| Table 13. USB Interrupt Register ( USBI, 01H )                             | 31 |

| Table 14. USB / Key board / AD Interrupt Enable Register ( USBKAIIE, 02H ) | 32 |

| Table 15. USB SIE Interface Register ( SIE1, 03H )                         |    |

| Table 16. Endpoint Index Register ( EPINDEX, 05H )                         | 34 |

| Table 17. Endpoint Control Register ( EPCON, 06H )                         | 35 |

| Table 18. Speaker / Watch-dog Timer Control Register ( SPWDCTL, 07H )      | 37 |

| Table 19. Transmit FIFO Data Register (TXDAT, 08H)                         | 38 |

| Table 20. Transmit FIFO Control Register (TXCON, 09H)                      |    |

| Table 21. Transmit FIFO Flag Register (TXFLG, 0AH)                         | 40 |

| Table 22. Transmit FIFO Byte Count Register (TXCNT, 0BH)                   |    |

| Table 23. Endpoint Transmit Status Register ( TXSTAT, 0CH )                | 43 |

| Table 24. PWM0 Duty Control Register ( PWM0, 0DH )                         | 45 |

| Table 25. PWM1 Duty Control Register ( PWM1, 0EH )                         | 46 |

| Table 26. Port2 Current Control Register ( P2ODCTL, 0FH )                  | 47 |

| Table 27. ISP program control Register ( ISP_CTL, 11H )                    | 48 |

| Table 28. ISP Address low byte Register ( ISPADDL, 12H )                   | 49 |

| Table 29. ISP Address high byte Register ( ISPADDH, 13H )                  | 50 |

| Table 30. ISP program data Register ( ISPDATA, 14H )                       | 51 |

| Table 31. AD / PWM function control Register ( ADPWM_C, 15H )              | 52 |

| Table 32. ADC Clock Control Register ( ADCLK, 16H )                        |    |

| Table 33. Kay borad / AD Interrupt Register ( KYADI, 17H )                 |    |

| Table 34. Receive FIFO Data Register (RXDAT, 18H)                          | 55 |

| Table 35. Receive FIFO Control Register (RXCON, 19H)                       | 56 |

|                                                                            |    |

| Table 37. Receive FIFO Byte Count Register (RXCNT, 1BH)       | 59 |

|---------------------------------------------------------------|----|

| Table 38. Endpoint Receive Status Register ( RXSTAT, 1CH )    | 60 |

| Table 39. ADC Lower Byte Data Register (ADL, 1DH)             | 63 |

| Table 40. ADC Higer Byte Data Register ( ADH, 1EH )           | 64 |

| Table 41. Push-pull DA speaker output envelope (SPKENV0, 10H) | 65 |

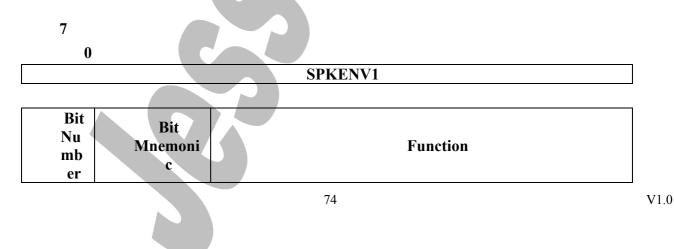

| Table 42. Push-pull DA speaker output envelope (SPKENV1, 1FH) | 65 |

| Table 43. DC Electrical Characteristics.                      | 66 |

| Table 44. Absolute Maximum Rating                             | 67 |

| Table 45. AC Electrical Characteristics.                      | 6  |

5

# 1. General Description

The WT65F4 is single chip Micro-controller with low speed Universal Serial Bus (USB) and A/D functions. It includes an 8-bit 8051 CPU core, 256 bytes SRAM, 8K Bytes Flash memories, 4K boot/ICE ROM, and 32 Programmable I/O. Build-in USB and ND function suitable for UPS, touch pad, joystick & digital board application.

# 2. Features

- 8051 CPU core

- Internal Oscillator circuit for crystal from 0.5MHz, 1MHz, 2MHz, 4MHz, 6MHz, 8MHz to 12MHz

- 256 bytes SRAM

- 4K byte Internal ROM for ISP and software ICE function use

- 8K bytes Flash Memory

- 4 flash programming modes: parallel, 2-wire ISP, ICE, and normal mode (USB download and RS232 download).

- 32 programmable I/O pins

- 8-pin key wake up function

- Full duplex serial bus for synchronous or asynchronous

- Embedded USB function with three endpoints (one control Enpoint0, two Interrupt IN endpoint)

- Watchdog timer (222 clock cycles time)

- Two 16-bit programmable timers

- Two-channel 8-bit programmable PWM

- ADPCM push-pull DA

- Seven-channel 12-bits rail-to-rail ND converters

- Low VDD reset at 3.5V 3.7V

- Power on reset

- Support power down/idle power management

- Integrated 3.3V power regulator for USB use

- CMOS technology for Iow power consumption

- Total 4 ports with 25mA Source Current and 8 ports with 25mA Sink Current

- DIP-40, LQFP-48, SDIP-28 or SOP-28 package

WT65F4 USB µC with 8KB ISP Flash memory & 12bit ADC

# **3.**Package information

| <u>Table 1. W 10514 Lackage Types</u> |             |  |  |  |  |  |

|---------------------------------------|-------------|--|--|--|--|--|

| Package Type                          | Part Number |  |  |  |  |  |

| LQFP 48                               | WT65F4-Q48  |  |  |  |  |  |

| DIP 28                                | WT65F4-N28  |  |  |  |  |  |

| DIP 40                                | WT65F4-N40  |  |  |  |  |  |

| SOP 28                                | WT65F4-S28  |  |  |  |  |  |

#### Table 1.WT65F4 Package Types

# 4.Pin Assignment and Description

Table 2. Pin Descriptions

| P  | in No | <b>).</b> | Pin Name | I/O | Description                                                        |

|----|-------|-----------|----------|-----|--------------------------------------------------------------------|

| 48 | 40    | 28        | Pin Mame | I/U | Description                                                        |

| 46 | 1     |           | P1.0     | I/O | General purpose I/O with pull-up resister                          |

| 47 | 2     |           | P1.1     | I/O | General purpose I/O with pull-up resister                          |

| 48 | 3     |           | P1.2     | I/O | General purpose I/O with pull-up resister                          |

| 1  | 4     |           | P1.3     | I/O | General purpose I/O with pull-up resister                          |

| 2  | 5     |           | P1.4     | I/O | General purpose I/O with pull-up resister                          |

| 3  | 6     |           | P1.5     | I/O | General purpose I/O with pull-up resister                          |

| 4  | 7     |           | P1.6     | I/O | General purpose I/O with pull-up resister                          |

| 5  | 8     |           | P1.7     | I/O | General purpose I/O with pull-up resister                          |

| 6  | 9     | 25        | RESET    | Ι   | Active High external Reset input                                   |

| 7  | 10    | 26        | P30/RXD  | I/O | General purpose I/O with pull-up resister/serial bus receive port  |

| 8  | 11    | 27        | P31/TXD  | I/O | General purpose I/O with pull-up resister/serial bus transmit port |

| 9  | 12    | 28        | P32/INT0 | I/O | General purpose I/O with pull-up resister/external interrupt 0     |

| 10 | 13    | 1         | P33/INT1 | I/O | General purpose I/O with pull-up resister/external interrupt 1     |

| 11 | 14    | 2         | P34/T0   | I/O | General purpose I/O with pull-up resister/Timer 0 external input   |

| 12 | 15    | 3         | P35/T1   | I/O | General purpose I/O with pull-up resister/Timer 1 external input   |

| 13 | 16    | 4         | P36/PWM0 | I/O | General purpose I/O with pull-up resister/PWM0 output              |

|    |       |           |          |     | 7                                                                  |

WT65F4 USB µC with 8KB ISP Flash memory & 12bit ADC

| -  |    |   |          |     |                                                       |

|----|----|---|----------|-----|-------------------------------------------------------|

| 14 | 17 | 5 | P37/PWM1 | I/O | General purpose I/O with pull-up resister/PWM1 output |

| 15 |    |   | VSS      | Ι   | Power Ground for DAC                                  |

| 16 |    |   | DAOUT0   | 0   | DAC output 0                                          |

| 17 |    |   | DAOUT1   | 0   | DAC output 1                                          |

| 18 |    |   | VDD      | Ι   | Power Source for DAC                                  |

| 19 | 18 | 6 | XTAL2    | 0   | Oscillator output                                     |

| 20 | 19 | 7 | XTAL1    | Ι   | Oscillator input                                      |

| 21 | 20 | 8 | VSS      | Р   | Power ground                                          |

|    |    |   |          |     |                                                       |

| 22 2                                                                                                                                                                 | 21                               | 9        | P20/AD0                                                                            | I/O                                                                    | General Purpose I/O with pull-up resistor/ADC channel 0 (25mA Source/Sink current)                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------|------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                      |                                  |          |                                                                                    |                                                                        | General Purpose I/O with pull-up resistor/ADC channel 1                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 23 2                                                                                                                                                                 | 22                               | 10       | P21/AD1                                                                            | I/O                                                                    | (25mA Source/Sink current)                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 24                                                                                                                                                                   | 22                               | 11       |                                                                                    | I/O                                                                    | General Purpose I/O with pull-up resistor/ADC channel 2                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 24 2                                                                                                                                                                 | 23                               | 11       | P22/AD2                                                                            | I/O                                                                    | (25mA Source/Sink current)                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 25 2                                                                                                                                                                 | 24                               | 12       | P23/AD3                                                                            | I/O                                                                    | General Purpose I/O with pull-up resistor/ADC channel 3                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 23 2                                                                                                                                                                 | 24                               | 12       | F25/AD5                                                                            | 1/0                                                                    | (25mA Source/Sink current)                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 26 2                                                                                                                                                                 | 25                               | 13       | P24/AD4                                                                            | I/O                                                                    | General Purpose I/O with pull-up resistor/ADC channel 4                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 20 2                                                                                                                                                                 | 23                               | 15       | 12 1/10                                                                            | 1/0                                                                    | (25mA Source/Sink current)                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 27 2                                                                                                                                                                 | 26                               | 14       | P25/AD5                                                                            | I/O                                                                    | General Purpose I/O with pull-up resistor/ADC channel 5                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                      |                                  |          | 1 20/1120                                                                          | 2/ 0                                                                   | (25mA Source/Sink current)                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 28 2                                                                                                                                                                 | 27                               | 15       | P26/AD6                                                                            | I/O                                                                    | General Purpose I/O with pull-up resistor/ADC channel 6                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                      |                                  |          |                                                                                    |                                                                        | (25mA Source/Sink current)                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 29 2                                                                                                                                                                 | 28                               | 16       | P27/Advref                                                                         | I/O                                                                    | General Purpose I/O with pull-up resistor/ADC reference                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2) 2                                                                                                                                                                 |                                  |          |                                                                                    |                                                                        | Voltage (75m & Source/Sink current)                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                      |                                  | 17       | DM                                                                                 |                                                                        | voltage (25mA Source/Sink current)                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 30 2                                                                                                                                                                 | 29                               | 17       | DM                                                                                 | I/O                                                                    | USB D-signal                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 30 2                                                                                                                                                                 |                                  | 17<br>18 | DM<br>DP                                                                           |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 30     2       31     3                                                                                                                                              | 29                               |          |                                                                                    | I/O                                                                    | USB D-signal                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 30         2           31         3           32         3                                                                                                           | 29<br>30                         | 18       | DP                                                                                 | I/O<br>I/O                                                             | USB D-signal<br>USB D + signal                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 30       2         31       3         32       3         33       3                                                                                                  | 29<br>30<br>31                   | 18       | DP<br>V33                                                                          | I/O<br>I/O<br>P                                                        | USB D-signal<br>USB D + signal<br>3.3V power regulation output                                                                                                                                                                                                                                                                                                                                                                                                          |

| 30         2           31         3           32         3           33         3           34         3                                                             | 29<br>30<br>31<br>32             | 18       | DP<br>V33<br>P07/K17                                                               | I/O<br>I/O<br>P<br>I/O                                                 | USB D-signal<br>USB D + signal<br>3.3V power regulation output<br>General Purpose IO with pull-up resistor/key interrupt                                                                                                                                                                                                                                                                                                                                                |

| 30         2           31         3           32         3           33         3           34         3           35         3                                      | 29<br>30<br>31<br>32<br>33       | 18       | DP<br>V33<br>P07/K17<br>P06/K16                                                    | I/O<br>I/O<br>P<br>I/O<br>I/O                                          | USB D-signal<br>USB D + signal<br>3.3V power regulation output<br>General Purpose IO with pull-up resistor/key interrupt<br>General Purpose IO with pull-up resistor/key interrupt                                                                                                                                                                                                                                                                                      |

| 30       2         31       3         32       3         33       3         34       3         35       3                                                            | 29<br>30<br>31<br>32<br>33<br>34 | 18       | DP<br>V33<br>P07/K17<br>P06/K16<br>PO5/K15                                         | I/O<br>I/O<br>P<br>I/O<br>I/O<br>I/O                                   | USB D-signal<br>USB D + signal<br>3.3V power regulation output<br>General Purpose IO with pull-up resistor/key interrupt<br>General Purpose IO with pull-up resistor/key interrupt<br>General Purpose IO with pull-up resistor/key interrupt                                                                                                                                                                                                                            |

| 30       2         31       3         32       3         33       3         34       3         35       3         36       3                                         | 29<br>30<br>31<br>32<br>33<br>34 | 18       | DP<br>V33<br>P07/K17<br>P06/K16<br>PO5/K15<br>P04/K14                              | I/O<br>I/O<br>P<br>I/O<br>I/O<br>I/O<br>I/O                            | USB D-signal<br>USB D + signal<br>3.3V power regulation output<br>General Purpose IO with pull-up resistor/key interrupt<br>General Purpose IO with pull-up resistor/key interrupt<br>General Purpose IO with pull-up resistor/key interrupt<br>General Purpose IO with pull-up resistor/key interrupt                                                                                                                                                                  |

| 30         2           31         3           32         3           33         3           34         3           35         3           36         3           37  | 29<br>30<br>31<br>32<br>33<br>34 | 18       | DP<br>V33<br>P07/K17<br>P06/K16<br>PO5/K15<br>P04/K14<br>ICE_N                     | I/O<br>I/O<br>P<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O                     | USB D-signal<br>USB D + signal<br>3.3V power regulation output<br>General Purpose IO with pull-up resistor/key interrupt<br>General Purpose IO with pull-up resistor/key interrupt<br>General Purpose IO with pull-up resistor/key interrupt<br>General Purpose IO with pull-up resistor/key interrupt<br>ICE mode input with internal pull-up. Active low.                                                                                                             |

| 30       2         31       3         32       3         33       3         34       3         35       3         36       3         37       38                     | 29<br>30<br>31<br>32<br>33<br>34 | 18       | DP<br>V33<br>P07/K17<br>P06/K16<br>PO5/K15<br>P04/K14<br>ICE_N<br>ICESTOP_N        | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I<br>I                       | USB D-signal<br>USB D + signal<br>3.3V power regulation output<br>General Purpose IO with pull-up resistor/key interrupt<br>General Purpose IO with pull-up resistor/key interrupt<br>General Purpose IO with pull-up resistor/key interrupt<br>General Purpose IO with pull-up resistor/key interrupt<br>ICE mode input with internal pull-up. Active low.<br>Run interrupt in ICE mode with pull-up resistor. Active low                                              |

| 30       2         31       3         32       3         33       3         34       3         35       3         36       3         37       38         39       40 | 29<br>30<br>31<br>32<br>33<br>34 | 18       | DP<br>V33<br>P07/K17<br>P06/K16<br>PO5/K15<br>P04/K14<br>ICE_N<br>ICESTOP_N<br>P41 | I/O<br>I/O<br>P<br>I/O<br>I/O<br>I/O<br>I/O<br>I<br>I<br>I<br>I<br>I/O | USB D-signal<br>USB D + signal<br>3.3V power regulation output<br>General Purpose IO with pull-up resistor/key interrupt<br>General Purpose IO with pull-up resistor/key interrupt<br>General Purpose IO with pull-up resistor/key interrupt<br>General Purpose IO with pull-up resistor/key interrupt<br>ICE mode input with internal pull-up. Active low.<br>Run interrupt in ICE mode with pull-up resistor. Active low<br>General Purpose IO with pull-up resistor. |

WT65F4 USB μC with 8KB ISP Flash memory & 12bit ADC

| 43 | 38 | 22 | P01/K11 | I/O | General Purpose IO with pull-up resistor/key interrupt |  |

|----|----|----|---------|-----|--------------------------------------------------------|--|

| 44 | 39 | 23 | P00/K10 | I/O | General Purpose IO with pull-up resistor/key interrupt |  |

| 45 | 40 | 24 | VDD     | Ι   | +5V power supply.                                      |  |

# 4.1 Pin Configuration

Figure 1. WT65F4 40-pin DIP & 28-pin SOP/DIP package

WT65F4 USB μC with 8KB ISP Flash memory & 12bit ADC

WT65F4 USB μC with 8KB ISP Flash memory & 12bit ADC

# **5.**Function Description

The WT65F4 is highly integrated Micro controller with Universal Bus (USB) interface. It contains an 8051 based CPU core, 8K bytes Flash memory, 256 bytes RAM,4K bytes boot / ICE ROM for 2-wire ISP and software ICE function, USB transceiver, Serial bus Interface Engine (SIE), System Interface Logic (SIL) and transmit / receive FIFOs. The USB function supports low-speed data rate (1.5M bps), suspend / resume mode, control / interrupt / bulk transfer and is fully compliant with the USB specification version 1.1.

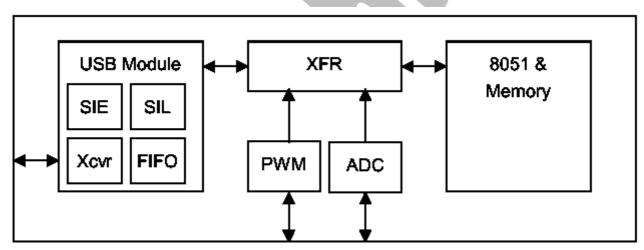

Operations of the USB interface and special function are controlled through the use of external function registers (XFRs), special function registers (SFRs), SIE, SIL, FIFOs and 8051 microcontroller that are described in the following sections. Figure 3 shows the main functional blocks of the WT65F4 USB module and how they interface with the 8051 CPU.

Figure 3.WT65F4 General Block Diagram

# 5.1 WT65F4 USB Module

The USB function interface manages communications between the Host PC and the USB function. The WT65F4 interface consists of the USB low-speed transceiver, the serial bus engine (SIE), the system interface logic (SIL), and the transmit and receive FIFOs. The USB low-speed transceiver provides the WT65F4 a physical interface to USB lines, the SIE handles communication protocol of USB, and the SIL

handles data transfers and provides the interface among the SIE, the 8051 CPU, the function FIFOs and

WT65F4 USB μC with 8KB ISP Flash memory & 12bit ADC

the matrix keyboard.

As shown in Figure 3, the main blocks in the USB module are:

1. Low Speed USB Transceiver: This block is an on-chip transceiver having one differential driver to

transmit the USB data onto the USB bus and single ended receivers on the D+ and D- lines as well as a differential receiver to receive the USB data signal on the USB bus.

2. Low / Full Serial Bus Interface Engine (SIE): The SIE does all the front end functions of USB

protocol such as clock/data separation, syncfield identification, NRZI-NRZ conversion, token packet decoding, bit stripping, bit stuffing, NRZ-NRZI conversion, CRC5 checking and CRC16 generation and checking. Besides, it manages detecting of reset, suspend and resume signals on the upstream port of the WT65F4 to wakeup the system from the suspend state. It also provides serial-to-parallel conversion for the serial packet from the Low Speed USB Transceiver to 8 bit parallel data to the System Interface Logic and

for 8 bit parallel data from the System Interface Logic to serial packet to the Low Speed USB Transceiver.

- 3. System Interface Logic (SIL): The SIL operates in conjunction with the 8051 CPU to provide the capabilities of controlling the operation of the FIFOs, monitoring the status of the data transactions, transferring event control to the 8051 CPU through interrupt requests at the appropriate moment, initiating resume signaling to USB bus while the WT65F4 is in powerdown mode. Operation of the SIL is controlled through the use of external function registers.

- 4. **USB Function FIFOs:** The WT65F4 function interface has three endpoints can support serveral types of USB data transfer: control, interrupt and bulk. Endpoint 0 contains one FIFO for transmit and receive, endpoint 1 and endpoint 2 have only one transmit FIFO. Transmit FIFOs are written by 8051 CPU, then read by SIL for transmission. Receive FIFO is written by the SIL following reception, then read by the 8051 CPU. Endpoint 0 supports control transfer for configuration / command / status type communication flows between client software and function. Endpoint 1 and endpoint 2 supports interrupt transfer.

WT65F4 USB μC with 8KB ISP Flash memory & 12bit ADC

## Figure 4. USB Interface Block Diagram

## 5.2 Microcontroller

The 8051 CPU is a high performance 8 bit on-chip microcontroller running the firmware associated with the operation of the function. It features a 8K-byte FLASH memory, a 256-byte RAM, a 4K-byte boot/ICE ROM, and two 16-bit timers. In addition, the 8051 has two power saving modes enabling further power reduction.

The 8051 CPU's operation speed is the same as the external clock frequency. The main blocks of the 8051 CPU are:

1. **Port 0:** Port 0 is an 8-bit bi-directional I/O port with internal pull-up. Port 0 is assigned as input after

reset (i.e., POOE = 00H). The input or output control is depend on the value of SFR POOE. When Port 0 is assigned as output, internal pull-up resistor must be disabled automatically. On the other

WT65F4 USB μC with 8KB ISP Flash memory & 12bit ADC

hand, when Port 0

is assigned as input, internal pull-up resistor can be disabled by setting bit 0 of register PUPCTL. Port 0 is also the multiplexed key interrupt and wake-up function during input status.

2. Port 1: Port 1 is an 8-bit bi-directional I/O port with internal pull-up. Port 1 is assigned as input after reset (i.e., P1OE = 00H). The input or output control is depend on the value of SFR P1OE. When Port 1 is assigned as output, internal pull-up resister must be disabled automatically. On the other hand, when Port 1

is assigned as input, internal pull-up resistor can be disabled by setting bit 1 of register PUPCTL.

3. Port 2: Port 2 is an 8-bit bi-directional I/O port with internal pull-up. Port 2 is assigned as input after reset (i.e., P2OE = 00H). The input or output control is depend on the value of SFR P2OE. When Port 2 is assigned as output or as AD purpose, internal pull-up resister must be disabled automatically. On the other

hand, when Port 2 is assigned as input, internal pull-up resistor can be disabled by setting bit 2 of register PUPCTL. Port 2 is also the multiplexed analog to digital converter (ADC) function during high-impedance inputs. To be an I/O port, the enhanced internal circuits can directly drive outside components such as LED, buzzer, etc. All of the ports can offer source and sink currents about 25mA.

4. Port 3: Port 3 is an 8-bit bi-directional I/O port with internal pull-up. Port 3 is assigned as input after reset (i.e., P3OE -- 00H). The input or output control is depend on the value of SFR P3OE. When Port 3 is assigned as output, internal pull-up resister must be disabled automatically. On the other hand, when Port 3

is assigned as input, internal pull-up resistor can be disabled by setting bit 3 of register PUPCTL. Port 3 also serves the functions of various special features as listed below:

| Port Pin | <b>Alternate Function</b>    |

|----------|------------------------------|

| P30      | RXD(serial input port)       |

| P31      | TXD(serial output port)      |

| P32      | INT0(external interrupt 0)   |

| P33      | INT1(external interrupt 1)   |

| P34      | T0 (timer 0 external input ) |

| P35      | T1 (timer 1 external input ) |

| P36      | PWM0 (PWM 0 output port)     |

| P37      | PWM1 (PWM 1 output port)     |

5. Port 4: Port 4 is an 2-bit bi-directional I/O port with internal pull-up. Port 4 is assigned as input

WT65F4 USB µC with 8KB ISP Flash memory & 12bit ADC

after reset (i.e., P4OE = 00H). The input or output control is depend on the value of SFR P4OE. When Port 4 is assigned as output, internal pull-up resister must be disabled automatically. On the other hand, when Port 4 is assigned as input, internal pull-up resistor can be disabled by setting bit 4 of register PUPCTL.

- 6. **16-bit Timer:** The WT65F4 has two 16 bits timers that can be clocked by Oscillator. It can be programmed for applications such as periodically generating interrupt or serving as a firmware watchdog timer etc.

- 7. **8051 On-Chip Memory:** The 8051 provides on-chip program memory beginning at location 4000H in normal mode, testing mode, and parallel programming mode. where, following chip reset, the first instruction is fetched and executed Flash memory. The 8051 CPU also provides on-chip data RAM beginning at location 00H. Locations 00H-7FH can be accessed with direct, indirect addressing while locations 80H-FFH can only be accessed with indirect addressing. In 2-wire ISP programming mode and ICE mode, the program memory begins at location 4000H. In ICE mode, the address is continuesly compared with both BRK0 and BRK1 SFR registers. If a match occurs, a breakpoint interrupt (i.e., NMI) is issured and the address is jumped to \$8010h.

| ROM Type                  | <b>Memory Location</b> |

|---------------------------|------------------------|

| Flash ROM 8K Byte         | 000h-1FFFh             |

| Boot boot/ICE ROM 4K Byte | 8000h-8FFFh            |

Figure 5. Memory mapping of Flash ROM, boot ROM, and ICE ROM

The following flash addresses are reserved for special purpose:

- \$0000h : program-reset vector.

- \$0003h : external interrupt 0, Key scan input or A/D interrupt vector.

- \$000Bh : timer 0 interrupt.

- \$0013h : external interrupt 1 or USB interrupt vector.

- \$001Bh : timer 1 interrupt.

- \$0023h : serial bus interrupts.

- \$8010h : breakpoint interrupt for ICE mode

# 5.3 Analog to Digital Converter (ADC)

The seven channels of 12-bits AD converter is turned on by ADON bit (Table 31). ADSEL0, 1, and 2 are the channel selected bits to control which channels' signal will be converted. The input analog signal will be converted to digital and stored in register ADH and ADL. As the ADINT\_IE (Table 14) being set to

WT65F4 USB μC with 8KB ISP Flash memory & 12bit ADC

"1" after AD be converted , interrupt occurs and ADINT (Table 13) is set to "1", AD block show in Figure 6.

Figure 7. ADC Timing Diagram

| Signals | I/O | Description                                                                        |

|---------|-----|------------------------------------------------------------------------------------|

| DAON    | Ι   | 0:Power-down mode;1:ADC turned on                                                  |

| ADEN    | Ι   | Conversion start. Rising edge trigger                                              |

| AD0~6   | Ι   | AD analog inputs                                                                   |

| ADVRF   | I   | AD reference voltage.1uF capacitor must be connected between ADVRF and VSS         |

| CLKIN   | L   | ADC clock input                                                                    |

| 1DH,1EH | 0   | AD digital output bus. Q is available from ADRDY rising edge to ADEN becoming low. |

| ADRDY   | 0   | AD output ready. Rising edge triggered                                             |

WT65F4 USB μC with 8KB ISP Flash memory & 12bit ADC

# 5.4 Pulse Width Modulation (PWM)

The corresponding PWM register (Table 24 and Table 25) controls the PWM duty cycle. Duty cycle ranges from 0/32 to 31/32. The LSB 3-bit of the PWM register determines the frame to be extended two Tosc (Tosc = 1/external clock frequency).

- 000 : no extended pulse.

- 001 : extended two Tosc at frame 4.

- 010 : extended two Tosc at frame 2 and 6.

- 011 : extended two Tosc at frame 2, 4 and 6.

- 100 : extended two Tosc at frame 1, 3, 5 and 7.

- 101 : extended two Tosc at frame 1, 3, 4, 5 and 7.

- 110 : extended two Tosc at frame 1,2, 3, 5, 6 and 7.

- 111 : extended two Tosc at frame 1, 2, 3, 4, 5, 6 and 7.

The MSB 5-bit of PWM register determines 0/32 to 31/32 duty cycle in each frame. However, both PWM0 and PWM1 duty cycles can be extended depending on the value of ADPWMCLK register. This can be done by dividing the external clock to the desired frequency (new Tosc), and then generate the pulse width according to the MSB 5-bit of PWM register. Figure 8 shows three examples of how PWM pulses are extended.

# 5.5 ADPCM push-pull DIA

Two voice envelope register buffers, SPKENV0 and SPKENV1, are added in XFR. If ADPCM is enabled (i.e., setting SPKON bit to high), P36/PWM0 and P37/PWM1 outputs the value from ADPCM push-pull DA. Otherwise, PWM output are selected. The bit DUALT indicates whether two envolope datas needs to be combined together in order to generate the dual tone.

Figure 9. ADPCM block diagram

# 5.6 WT65F4 Address Space Mapping

The WT65F4 has five address spaces: a program memory space, an internal data memory space, a special function register space, an external function register space, and a register file. Table 4 shows the addressing mapping if the WT65F4.

| Table 4. Addressing mapping |                 |                           |                                       |  |  |  |  |  |  |  |  |

|-----------------------------|-----------------|---------------------------|---------------------------------------|--|--|--|--|--|--|--|--|

| Memory Type                 | Size            | Location                  | Data<br>Addressing                    |  |  |  |  |  |  |  |  |

| Flash Code                  | 8K bytes        | 0000H-<br>1FFFH           | Indirect using<br>MOVC<br>instruction |  |  |  |  |  |  |  |  |

| External                    |                 |                           | Indirect using                        |  |  |  |  |  |  |  |  |

| Function                    | 32 bytes        | 00H-1FH                   | MOVX                                  |  |  |  |  |  |  |  |  |

| Register                    |                 |                           | instruction                           |  |  |  |  |  |  |  |  |

| Internal Data               | 128 bytes       | 00H-7FH                   | Direct, Indirect                      |  |  |  |  |  |  |  |  |

| Internal Data               | 128 bytes       | 80H-FFH                   | Indirect                              |  |  |  |  |  |  |  |  |

| SFRs                        | 128 bytes       | 80H-FFH                   | Direct                                |  |  |  |  |  |  |  |  |

| Register File               | 8 bytes         | R0-R7                     | Register                              |  |  |  |  |  |  |  |  |

| Note : Direct :             | Direct Byte A   | ddressing                 |                                       |  |  |  |  |  |  |  |  |

| Indirect:                   | Indirect Byte   | Addressing                |                                       |  |  |  |  |  |  |  |  |

| (1):                        | Please refer to | 8051 data sheet for bit d | lefinition of each SFR.               |  |  |  |  |  |  |  |  |

## Table 4. Addressing mapping

# 5.7 WT65F4 Special Function Register Address Space

The special function registers (SFRs) reside in this optimized 8051 microcontroller Core. Table 5

WT65F4 USB µC with 8KB ISP Flash memory & 12bit ADC

lists the location of all the WT65F4 SFRs. Please refer to the 8051 Data sheet for bit definition of each SFR.

|        |   | -      |       | P      | P      | P      | P        | P            |         |        | P      |

|--------|---|--------|-------|--------|--------|--------|----------|--------------|---------|--------|--------|

| Na     | A | R      | initi | В      | В      | В      | В        | В            | Bi      | В      | В      |

| me     | 0 | /      | al    | it     | it     | it     | it       | it           | t       | it     | it     |

|        | 0 | V      | a1    | 7      | 6      | 5      | 4        | 3            | 2       | 1      | 0      |

|        |   |        |       | Р      | п      | n      | D        | р            |         | п      | р      |

| DO     | 8 | R<br>V |       | 0      | Р      | P      | P        | P            | P0      | P      | P      |

| P0     |   | V      | FFh   |        | 0.     | 0.     | 0.       | 0.           | .2      | 0.     | 0.     |

|        | ľ |        |       | 7      | 6      | 5      | 4        | 3            |         | 1      | 0      |

|        | 8 | n      |       |        |        |        |          |              |         |        |        |

| SP     | 1 | R<br>V | 07h   |        |        |        |          |              |         |        |        |

|        | ł | V      |       |        |        |        |          |              |         |        |        |

|        | 8 |        |       |        |        |        |          |              |         |        |        |

| DP     |   | v      | 00h   |        |        |        |          |              |         |        |        |

| L      | ŀ |        | 0011  |        |        |        |          |              |         |        |        |

|        | 8 |        |       |        |        |        |          |              |         |        |        |

| DP     |   | v      | 00h   |        |        |        |          |              |         |        |        |

| Н      | ł |        | 0011  |        |        |        |          |              |         |        |        |

|        |   |        |       | Р      | Р      | Р      | Р        | Р            |         | Р      | Р      |

|        | 8 |        |       | 0      | 0      | 0      | 0        | 0            | PO      | 0      | 0      |

| PO     |   | v      | 00h   | 7      | 6      | 5      | 4        | 3            | 2       | 1      | 0      |

| OE     | 1 | •      | 0011  | Ó      | Ŏ      | 0      | O O      | 0            | 0       | 0      | Ŏ      |

|        | 1 |        |       | E      | E      | E      | E        | E            | Е       | E      | E      |

|        |   |        |       | S      |        |        | I        |              |         | L      |        |

| PC     | 8 | R      | 0x01  | M      |        | S      | C        | G            | G       | Р      | Ι      |

| 0      | 7 | V      | 0000  | O IVI  |        | P      | E        | F            | F0      | D      | D      |

| Ν      | ł | v      | b     | D      |        | M      |          | 1            | 10      | D      | L      |

| ТС     |   |        |       | T T    | Т      | T      | (1)<br>T | Ι            |         | Ι      | Ι      |

| 0      |   | R      | 00h   | F      | R      | I<br>F | R        | E I          | IT      | E I    | T<br>T |

| N N    | 1 | V      | 0011  | г<br>1 | к<br>1 | Г<br>0 | 0 K      | <u></u><br>1 | 1       | Е<br>0 | 1<br>0 |

| T T    | 1 |        |       | G      |        | 0      | 0        | G            |         | 0      | U      |

| I<br>M | 8 | מ      |       |        | C      | М      | М        |              |         | М      | М      |

| O M    | 9 | R<br>V | 00h   | A<br>T | /      |        | M        | A            | C/<br>T | M 1    |        |

|        | ł | v      |       | E      | Т      | 1      | 0        | T            |         | 1      | 0      |

| DE     |   |        |       |        |        | т      | т        | E            |         | т      | т      |

| TT     | 8 | т      |       | Т      | Т      | Т      | Т        | Т            | Т       | Т      | Т      |

| TL     |   | R<br>V | 00h   | L      | L      | L      | L        | L            | L       | L      | L      |

| 0      | ł | V      |       |        | 0      | 0      | 0        | 0            | 02      | 0      | 0      |

|        |   |        |       | 7      | 6      | 5      | 4        | 3            |         | 1      | 0      |

| TH     |   | R      | 00h   | T      | Т      | Т      | Т        | Т            | Т       | Т      | Т      |

| 0      |   | V      |       | Н      | Н      | Н      | Н        | Н            | Н       | Н      | Н      |

# Table 5. WT65F4 Special Function Register (SFR) layout

20

⑧ Jess Technology Co., Ltd.

▶ 氏科技有限公司

Suites 2202-7, 22/F, Tower 6, The Gateway, 9 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel (852) 2123 3289 Fax (852) 2123 3393 E-mail: <u>sales@jesstech.com</u> HomePage: http://www.jesstech.com

WT65F4 USB  $\mu C$  with 8KB ISP Flash memory & 12bit ADC

|    | ł   |   |       | 0 | 0      | 0  | 0   | 0   | 02      | 0      | 0      |

|----|-----|---|-------|---|--------|----|-----|-----|---------|--------|--------|

|    | 1   |   |       | 7 | 6      | 5  | 4   | 3   | 02      | 1      | 0      |

|    |     |   |       | Ť | T      | T  | T   | T   |         | T      | T      |

| TL | 8   | R |       | Ĺ | L      | Ĺ  | Ĺ   | L   | Т       | L      | L      |

| 1  | (   | v | 00h   | 1 | 1      | 1  | 1   | 1   | L       | 1      | 1      |

| 1  | ł   | • |       | 7 | 6      | 5  | 4   | 3   | 12      | 1      | 0      |

|    |     |   |       | Ť | T      | T  | T   | T   |         | T      | T T    |

| TH | 8   | R |       | H | H      | H  | H   | H   | Т       | Η      | H      |

| 1  | I   | v | 00h   | 1 | 1      | 1  | 1   | 1   | Н       | 1      | 1      |

| 1  | ł   | • |       | 7 | 6      | 5  | 4   | 3   | 12      | 1      | 0      |

|    |     |   |       | P |        |    |     |     |         |        |        |

|    | ç   | R |       | 1 | Р      | Р  | Р   | Р   | P1      | Р      | Р      |

| P1 | (   | v | FFh   |   | 1.     | 1. | 1.  | 1.  | .2      | 1.     | 1.     |

|    | ł   | • |       | 7 | 6      | 5  | 4   | 3   | .2      | 1      | 0      |

|    |     |   |       | P | Р      | Р  | Р   | Р   |         | Р      | Р      |

|    | d   |   |       | 1 | 1      | 1  | 1   | 1   | P1      | 1      | 1      |

| P1 | 1   | V | 00h   | 7 | 6      | 5  | 4   | 3   | 2       | 1      | 0      |

| OE | ŀ   | • | 0011  | Ó | 0<br>0 | 0  | - O | 0   | 0       | 0      | 0<br>0 |

|    | 1   |   |       | Ē | E      | E  | E   | E   | Е       | E      | E      |

| S  | C   |   |       | S | S      | S  | R   | T   | R       |        |        |

| M  | ŝ   | R | 00h   | M | M      | M  | E   | B   | B       | Т      | Т      |

| 2  | ł   | V | 0011  | 0 | 1      | 3  | N   | 8   | 8       | Ι      | Ι      |

|    | 4   |   |       |   |        |    |     |     | 0       |        |        |

| SB | ĺ   | R | XXh   | S | S      | S  | S   | S   | S2      | S      | S      |

| UF | ŀ   | ν | 21211 | 7 | 6      | 5  | 4   | 3   | 52      | 1      | 0      |

|    |     |   |       | Р |        |    | _   | _   |         | _      | _      |

|    | Ι   | R |       | 2 | Р      | Р  | Р   | Р   | P2      | Р      | Р      |

| P2 | (   | v | FFh   |   | 2.     | 2. | 2.  | 2.  | .2      | 2.     | 2.     |

|    | ł   | • |       | 7 | 6      | 5  | 4   | 3   | .2      | 1      | 0      |

|    |     |   |       | P | Р      | Р  | Р   | Р   |         | Р      | Р      |

|    |     |   |       | 2 | 2      | 2  | 2   |     | P2<br>2 | 2      | 2      |

| P2 | 2   | v | 00h   | 7 | 6      | 5  | 4   | 23  |         | 2<br>1 | 2<br>0 |

| OE | ŀ   | • | 0011  | Ó | Ů      | 0  | 0   | 0   | 0       | 0      | 0      |

|    |     |   |       | Ē | E      | Ē  | Ē   | Ē   | E       | E      | Ē      |

|    |     |   | 0xx0  |   |        |    |     | E   | Е       | E      | E      |

| IE | 8   | R | 0000  | E |        |    | E   | T   | X       | T      | X      |

| 0  | ł   | V | b     | Α |        |    | S   | 1   | 1       | 0      | 0      |

|    |     |   |       | Р | n      |    |     |     | _       |        |        |

|    | ł   | R |       | 3 | P      | Р  | P   | P   | P3      | P      | P      |

| P3 | (   | V | FFh   |   | 3.     | 3. | 3.  | 3.  | .2      | 3.     | 3.     |

|    | ł   |   |       | 7 | 6      | 5  | 4   | 3   |         | 1      | 0      |

|    |     |   |       | P | Р      | Р  | Р   | Р   | 50      | Р      | Р      |

|    | F   |   |       |   | 3      | 3  | 3   | 3   | P3      | 3      | 3      |

| P3 | 4   | v | 00h   | 3 | 6      | 5  | 4   | 3   | 2       | 1      | 0      |

| OE | ŀ   |   |       | 0 | Ő      | 0  | 0   | 0   | 0       | 0      | Ô      |

|    |     |   |       | Ē | Ē      | Ē  | Ē   | Ē   | Е       | Ē      | Ē      |

| IP | F   | R | XXXX  |   |        |    | P   | P   | Р       | P      | P      |

|    | - 1 | - |       |   | l      | I  | · · | · · | · ·     | · ·    | · ·    |

⑧ Jess Technology Co., Ltd.

▶ 氏科技有限公司

Suites 2202-7, 22/F, Tower 6, The Gateway, 9 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel (852) 2123 3289 Fax (852) 2123 3393 E-mail: <u>sales@jesstech.com</u> HomePage: http://www.jesstech.com

WT65F4 USB μC with 8KB ISP Flash memory & 12bit ADC

| 0        | 8        | V      |              |        |         |              | S            | Т           | X                 | Т           | Х            |

|----------|----------|--------|--------------|--------|---------|--------------|--------------|-------------|-------------------|-------------|--------------|

|          | <u>}</u> |        | b            |        |         |              | D            | 1<br>P      | 1                 | 0           | 0            |

| PS       | 1        | R<br>V |              | C      | A       | F            | R<br>S       | R<br>S<br>O | O<br>V            |             | Р            |

| W        | ł        | V      |              | Y      | C       | 0            | 1            | 0           | V                 |             | D            |

| P4(      | 1<br>8   | R      |              |        |         |              |              |             |                   | P<br>4      | Р<br>4       |

| 2)       | ł        | V      | b            |        |         |              |              |             |                   | 4           | 0            |

|          | т        |        |              |        |         |              |              |             |                   | P           | P            |

| P4       |          | V      | xxxx<br>xx00 |        |         |              |              |             |                   | 4           | 4<br>0       |

| OE       | ł        |        | b            |        |         |              |              |             |                   | 0           | 0            |

|          |          |        |              | A      |         |              |              |             |                   | E           | E            |

| ٨        | I        | D      |              | C      | A<br>C  | A            | A            | A<br>C      | A<br>C<br>C.<br>2 | A<br>C      | A<br>C<br>C. |

| A<br>CC  | (        | R<br>V | 00h          | С      | C C     | C<br>C<br>.5 | C<br>C<br>.4 | C<br>C      | C.                | C.          | C.           |

|          | 1        |        |              | 7      | .6      | .5           | .4           | C<br>.3     | 2                 | 1           | 0            |

| D        | I        | R      | 0.01         | В      | В       | В            | В            | В           | B.                | B.          | B.           |

| В        | C<br>ł   | V      | 00h          | 7      | .6      | .5           | .4           | .3          | 2                 | 1           | 0            |

| PC       | F        |        |              | Р      | Р       | Р            | Р            | Р           | Р                 | Р           | Р            |

| SK       | e        | R      | 00h          | C<br>C | C<br>C  | C<br>C<br>5  | C<br>C       | C<br>C      | C<br>C<br>2       | C<br>C<br>1 | C<br>C       |

| 0        | ł        |        |              | C<br>7 | 6       | 5            | 4            | 3           | 2                 | 1           | 0            |

| DC       | т        |        |              | P<br>C | P       | P<br>C       | P<br>C       | P<br>C      | Р                 | Р           | Р            |

| PC<br>SK | 1        | R      | 00h          | C      | C<br>C  | C<br>C       | C<br>C       | C<br>C      | C                 | C           | C            |

| 1        | ł        |        |              | 1      | 1       | 1            | 1            | 1           | C<br>10           | C<br>C<br>9 | C<br>C<br>8  |

|          |          |        |              | 5      | 4       | 3            | 2<br>P       | 1<br>P      |                   | P           | P            |

| PU       | I        |        |              |        |         |              | 4            | 3           | Р2<br>Р           | 1           | 0            |

| PC<br>TI | 0        | V      | 00h          |        | -       |              | P            | P           | U<br>U            | P           | P            |

| TL       | 1        |        |              |        |         |              | U<br>P       | U<br>P      | Р                 | U<br>P      | U<br>P       |

|          |          |        |              |        |         |              |              |             | B                 | В           | В            |

| BR<br>KE | I        | V      | 00h          |        |         |              |              |             | K<br>E            | K<br>E      | K<br>E       |

| N N      | ł        | v      | 001          |        |         |              |              |             | Ν                 | Ν           | Ν            |

|          |          |        |              |        |         |              |              |             | 2                 | 1           | 0            |

| BR       | I        |        | 0.01         | B<br>0 | B       | B            | B            | B           | В                 | В           | В            |

| K0<br>L  | ł        | V      | 00h          |        | 0.<br>6 | 0.<br>5      | 0.<br>4      | 0.<br>3     | 0.<br>2           | 0.<br>1     | 0.<br>0      |

| BR       |          |        |              | 7<br>B | B       | B            | В            | B           | B                 | B           | B            |

| K0       |          | V      | 00h          | В<br>0 | Б<br>0. | В<br>0.      | В<br>0.      | В<br>0.     | В<br>0.           | 0.          | 0.           |

| Н        | ł        |        |              |        | 1       | 1            | 1            | 1           | 10                | 9           | 8            |

WT65F4 USB µC with 8KB ISP Flash memory & 12bit ADC

|               |             |   |     | 1<br>5           | 4                 | 3                 | 2                 | 1                 |               |              |   |              |

|---------------|-------------|---|-----|------------------|-------------------|-------------------|-------------------|-------------------|---------------|--------------|---|--------------|

| BR<br>K1<br>L | H<br>I<br>I | V | 00h | B<br>1<br>7      | B<br>1.<br>6      | B<br>1.<br>5      | B<br>1.<br>4      | B<br>1.<br>3      | B<br>1.<br>2  | B<br>1.<br>1 |   | B<br>1.<br>0 |

| BR<br>K1<br>H | H<br>H<br>H | V | 00h | B<br>1<br>1<br>5 | B<br>1.<br>1<br>4 | B<br>1.<br>1<br>3 | B<br>1.<br>1<br>2 | B<br>1.<br>1<br>1 | B<br>1.<br>10 | B<br>1.<br>9 | v | B<br>1.<br>8 |

(1) Read only (2) Bit addressable

#### 5.8 **External Function Register Address Space**

The external function registers (XFRs) reside inside the USB module. The 8051 is connected to one of these registers when the register is addressed by the contents of registers R0 or R1 in the internal data memory. Two instructions, MOVX @Rr, A and MOVX A, @Rr can be used for data movement between the XFRs and accumulator of the 8051. Table 6 lists the location of all the XFRs. When the instruction, MOVX @Rr, A or MOVX A, @Rr, is executed, the address contained in R0 or R1 registers is latched by ALE signal and then the direction of data movement between the XFRs and the 8051 can be controlled by the signals WR or RD subsequently generated by the 8051.

| Na<br>me        |  | Init<br>ial       | Bi<br>t 7              | Bi<br>t 6                | Bi<br>t 5               | Bi<br>t 4                   | Bi<br>t 3                 | Bit<br>2              | Bi<br>t 1             | Bit<br>0              |

|-----------------|--|-------------------|------------------------|--------------------------|-------------------------|-----------------------------|---------------------------|-----------------------|-----------------------|-----------------------|

| FA<br>DD<br>R   |  | 00h               | -                      | A<br>D<br>R6             | A<br>D<br>R<br>5        | A<br>D<br>R<br>4            | A<br>D<br>R<br>3          | AD<br>R2              | A<br>D<br>R1          | A<br>DR<br>0          |

| US<br>BI        |  | xx0<br>000<br>00b |                        |                          | R<br>E S<br>U<br>M<br>E | S<br>U<br>SP<br>E<br>N<br>D | U<br>SB<br>x0<br>IN<br>T  | US<br>BTx<br>2IN<br>T | US<br>BT<br>x1I<br>NT | US<br>BT<br>x0I<br>NT |

| US<br>BK<br>AIE |  | 00h               | KI<br>N<br>T<br>I<br>E | A<br>DI<br>NT<br>_I<br>E | RE<br>SU<br>ME<br>_IE   | SU<br>PE<br>N<br>D_<br>IE   | Rx<br>0I<br>NT<br>_I<br>E | Tx2<br>INT<br>_IE     | Tx<br>1IN<br>T_I<br>Ē | Tx0<br>INT<br>_IE     |

| SIE<br>I        |  | Xx0<br>000        | Ţ                      |                          | L<br>V                  | CL<br>K1<br>2M              | V<br>33                   | US<br>BR<br>STE       | D<br>M                | W<br>A                |

|                 |  |                   |                        |                          | 23                      |                             |                           |                       |                       | V1.0                  |

#### Table 6. External Function Register (XFR) layout

WT65F4 USB μC with 8KB ISP Flash memory & 12bit ADC

|                     | Ob                     |                            |                        | R<br>E<br>N            | EN                         | E<br>N                     | N                 | E<br>N                 | KE<br>UP           |

|---------------------|------------------------|----------------------------|------------------------|------------------------|----------------------------|----------------------------|-------------------|------------------------|--------------------|

|                     |                        |                            |                        |                        |                            |                            |                   |                        |                    |

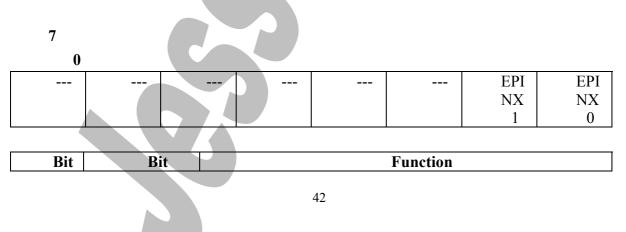

| EPI<br>ND<br>EX     | xxx<br>xxx<br>00b      |                            |                        |                        |                            |                            | ł                 | EP<br>IN<br>X1         | EP<br>IN<br>X0     |

| EP<br>CO<br>N       | 001<br>x01<br>01b<br>3 | R<br>X<br>S<br>T<br>L      | T<br>X<br>ST<br>L      | C<br>T<br>L<br>P       | -                          | R<br>XI<br>E               | RX<br>EP<br>EN    | T<br>X<br>O<br>E       | TX<br>EP<br>EN     |

| SP<br>WD<br>CT<br>L | 000<br>000<br>10h      | S<br>P<br>K<br>O<br>N      | D<br>U<br>A<br>LT      |                        |                            |                            |                   | E<br>N_<br>W<br>D<br>T | W<br>DT<br>RS<br>T |

| TX<br>CA<br>T       | xxh                    | T<br>X<br>D<br>A<br>T<br>7 | T<br>X<br>D<br>A<br>T6 | T<br>X<br>D<br>A<br>T5 | T<br>X<br>D<br>A<br>T<br>4 | T<br>X<br>D<br>A<br>T<br>3 | TX<br>DA<br>T2    | T<br>X<br>D<br>AT<br>1 | TX<br>D<br>AT<br>0 |

| TX<br>CO<br>N       | 0xx<br>xxx<br>xxb      | T<br>X<br>C<br>L<br>R      |                        | I                      |                            | 1                          |                   |                        |                    |

| TX<br>FL<br>G       | xxx<br>x10<br>00b      |                            |                        | I                      | 1                          | T<br>X<br>E<br>M<br>P      | TX<br>FU<br>LL    | T<br>X<br>U<br>RF      | TX<br>O<br>VF      |

| TX<br>CN<br>T       | 00h                    |                            | -                      |                        |                            | T<br>X<br>C<br>N<br>T<br>3 | TX<br>CN<br>T2    | T<br>X<br>C<br>N<br>T1 | TX<br>CN<br>T0     |

| TX<br>ST<br>AT      | 00h                    | T<br>X<br>S<br>E<br>Q      | -                      | -                      |                            |                            | TX<br>VO<br>ID    | T<br>X<br>E<br>RP      | TX<br>AC<br>K      |

| PW<br>M0            | 00h                    | P<br>W<br>M<br>07          | P<br>W<br>M<br>06      | P<br>W<br>M<br>05      | P<br>W<br>M<br>04          | P<br>W<br>M<br>03          | P<br>W<br>M<br>O2 | P<br>W<br>M<br>01      | P<br>W<br>M0<br>0  |

| PW<br>M1            | 00h                    | P<br>W<br>M<br>17          | P<br>W<br>M<br>16      | P<br>W<br>M<br>15      | P<br>W<br>M<br>14          | P<br>W<br>M<br>13          | P<br>W<br>M1<br>2 | P<br>W<br>M<br>11      | P<br>W<br>M1<br>0  |

| P0<br>OD<br>CT<br>L | 00h                    | , i                        |                        | P0<br>5S<br>N          | P0<br>4S<br>N              |                            |                   | P0<br>1S<br>N          | P0<br>0S<br>N      |

| SP<br>KE<br>NV<br>0 | 00h                    | D<br>A<br>0.<br>7          | D<br>A<br>0.<br>6      | D<br>A<br>0.<br>5      | D<br>A<br>0.<br>4          | D<br>A<br>0.<br>3          | DA<br>0.2         | D<br>A0<br>.1          | D<br>A0<br>.0      |

| ISP<br>CT<br>L      | xxh                    | X<br>E                     | Y<br>E                 | S<br>E                 | O<br>S                     | E<br>R<br>A<br>S<br>E      | PR<br>OG          | M<br>A<br>S1           | N<br>VS<br>TR      |

| ISP<br>AD<br>DL     | xxh                    |                            |                        |                        | Y<br>A<br>D                | Y<br>A<br>D                | Y<br>A<br>D       | Y<br>A<br>D            | Y<br>A<br>D        |

WT65F4 USB  $\mu C$  with 8KB ISP Flash memory & 12bit ADC

|                 |  |     |                                       |                                   |                                   | R<br>4/<br>A<br>4                | R<br>3/<br>A<br>3                | R2<br>/A<br>2                | R<br>1/<br>A<br>1                | R0<br>/A<br>0                |

|-----------------|--|-----|---------------------------------------|-----------------------------------|-----------------------------------|----------------------------------|----------------------------------|------------------------------|----------------------------------|------------------------------|